AD9547针对许多系统提供同步功能,包括同步光纤网络(SONET/SDH)。该器件产生的输出时钟可以与两路差分或四路单端外部输入参考时钟之一同步。数字锁相环(PLL)

2025-04-11 09:37

很多激光器只能基于内部时钟信号触发脉冲输出。这类激光器不能通过一个外部信号(比如Aerotech的位置同步输出PSO功能)异步触发。针对这类激光器的一种解决方法是把PSO输出

2021-03-19 14:57

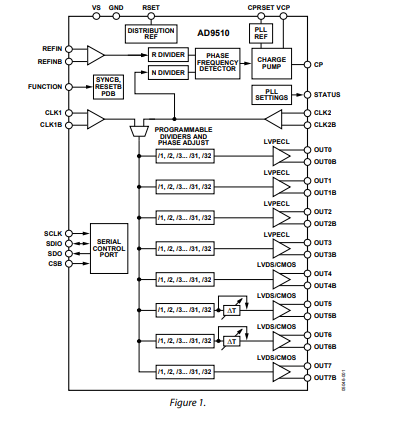

AD9510提供多路输出时钟分配功能,并集成一个片内锁相环(PLL)内核。它具有低抖动和低相位噪声特性,能够极大地提升数据转换器的时钟性能。4路独立的LVPECL时钟

2025-04-15 11:41

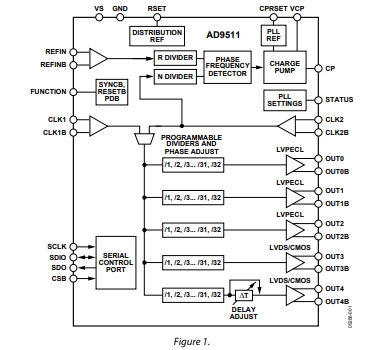

AD9511提供多路输出时钟分配功能,并集成一个片内锁相环(PLL)内核。它具有低抖动和低相位噪声特性,能够极大地提升数据转换器的时钟性能。3路独立的LVPECL时钟

2025-04-15 13:48

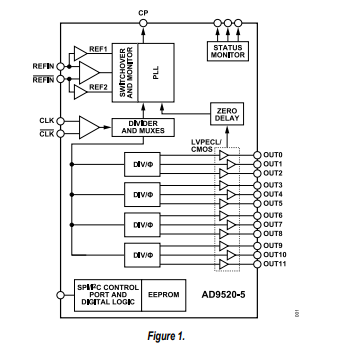

AD9520-5提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL),可以配合外部VCO使用。

2025-04-11 11:17

一般情况下,FPGA器件内部的逻辑会在每个时钟周期的上升沿执行一次数据的输入和输出处理,而在两个时钟上升沿的空闲时间里,则可以用于执行各种各样复杂的处理。而一个比较耗时的复杂运算过程,往往无法一个

2018-05-23 05:56

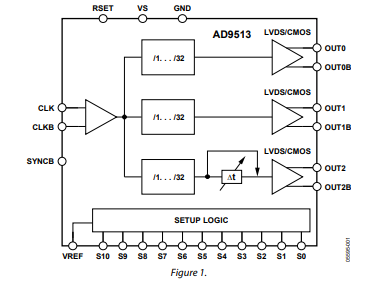

AD9513是一款三路输出时钟分配IC,其低抖动和低相位噪声特性能够实现优质的数据转换器性能。这款器件也适合于对相位噪声和抖动有严格要求的其它应用。 三路独立的时钟输出

2025-04-15 10:57

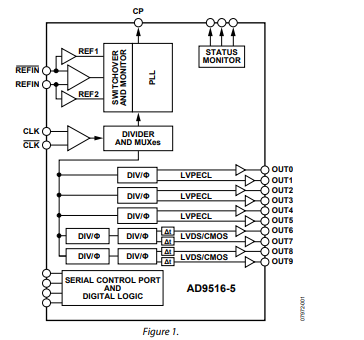

AD9516-5提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL),可以配合外部VCO/VCXO使用。

2025-04-11 11:00

时钟周期也称为振荡周期,定义为时钟频率的倒数。时钟周期是计算机中最基本的、最小的时间单位。在一个时钟周期内,CPU仅完成一个最基本的动作。

2018-03-11 10:07