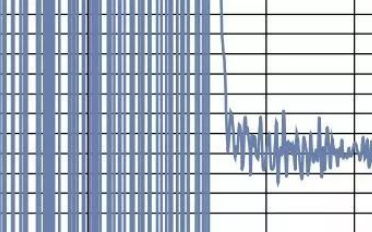

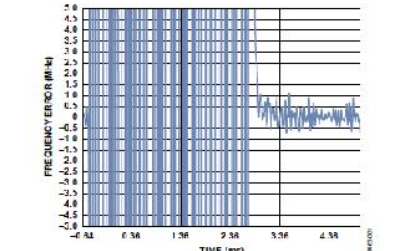

当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的

2018-03-14 15:17

pll锁定时间按照频率精度多少来计算 PLL锁定时间是指当PLL尝试将输出频率与输入频率相匹配时所需的

2023-09-02 15:12

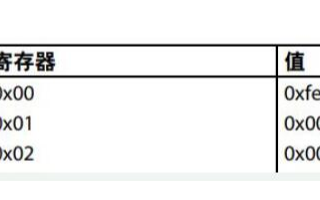

按照上述步骤校准完成后,PLL 的反馈操作使 VCO 锁定于正确的频率。锁定速度取决于非线性周跳行为。PLL总锁定时间包

2018-05-18 08:35

本文以高度集成的解调器和频率合成器 ADRF6820 为例,告诉大家如何手动选择频段以缩短PLL锁定时间。

2020-09-01 11:34

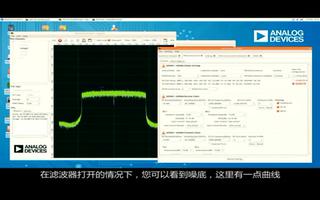

AD9361芯片工作频率范围为70 MHz至6 GHz,涵盖大部分特许执照和免执照频段,通过对AD9361自身可编程改变采样速率、数字滤波器和抽取参数,使该芯片支持的通道带宽范围为低于200 kHz到56 MHz。

2021-03-09 11:47

AD9361是一种宽频带软件可定义收发器芯片,由ADI(Analog Devices Inc.)公司研发,可用于各种射频(RF)应用。它是一种全集成的射频收发器,实现了收发器功能。在这篇文章中,我们

2023-12-26 15:49

AD9361射频捷变收发器概述,包括从RF到基带的RX和TX信号路径、自动增益控制(AGC)、RF PLL和本振(LO)生成。 AD9361射频捷变收发器概述:http

2018-06-05 13:45

使用自动校准模式时,总锁定时间对某些应用来说可能太长。 本应用笔记提出一种通过手动选择频段来显著缩短锁定时间的方案

2021-06-21 09:53

频谱分析仪通常用于测量信号的频谱特性,如频率、幅度和相位等。在某些应用中,频谱分析仪也可以用来测量相位锁定环( PLL)的锁定时间。

2024-05-17 16:14

锁相环锁定时间取决于哪些因素?如何加速锁定? 锁相环(PLL)是一种常见的电路,用于稳定频率。PLL中的关键是相锁。相锁发挥着将输入频率与参考频率调整到相等的重要作用。

2023-10-30 10:51