如何实现高速时钟信号的差分布线 在高速设计中,如何解决信号的完整性问题?差分布线方式是如何实现的?对于只有一个输出端的时钟信号线,如何实现

2009-04-15 00:26

一站式PCBA智造厂家今天为大家讲讲PCB设计差分布线有什么要求?PCB设计差分布线要求及操作技巧。高速串行总线的普及,使得PCB板上

2023-07-07 09:25

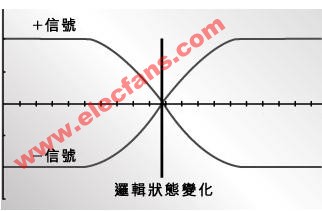

高速串行总线的普及,使得PCB板上差分信号越来越多,那么,PCB板如何差分布线? 各类差分线的阻抗要求不同,根据设计要求,通过阻抗计算软件计算出差分阻抗和对应的线 宽间

2020-12-04 11:14

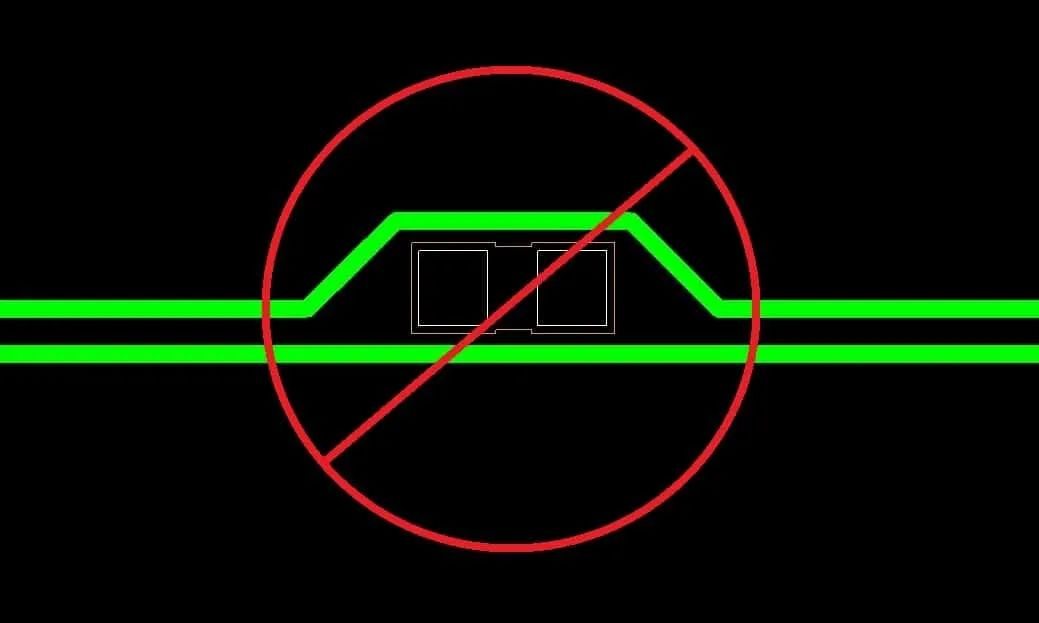

高速差分布线最佳实践:对称地布置差分对,并保持信号平行。不包括差分器之间的任何组件或通孔。对称地放置耦合电容器

2022-10-25 10:36

对于只有一个输出端的时钟信号线,如何实现差分布线? 在设计电路或系统时,差分信号线被广泛应用于传输时钟信号。差分信号线可以有效地抵抗噪声、串扰和损耗,从而提高信号完整性

2023-11-24 14:32

高效差分对布线指南:提高 PCB 布线速度

2023-11-29 16:00

电路板设计过程中采用差分信号线布线的优势和布线技巧 布线

2009-09-06 08:20

本文要点PCB差分对的基础知识。差分对布线指南,实现更好的布线设计。高效利用PCB设计工具。“众人拾柴火焰高”——资源整合通常会带来更好的结果。毕竟“三个臭皮匠,顶个诸

2022-12-05 11:06 深圳(耀创)电子科技有限公司 企业号

为何差分对的布线要靠近且平行? 差分对是一种电路设计中常见的布线方式,它的作用是减小信号传输的干扰和噪音。差分信号传输是

2023-11-24 14:38

布线非常靠近的差分信号对相互之间也会互相紧密耦合,这种互相之间的耦合会减小EMI发射,差分信号线的主要缺点是增加了PCB的面积,本文介绍电路板设计过程中采用差分信号线

2017-12-11 15:47