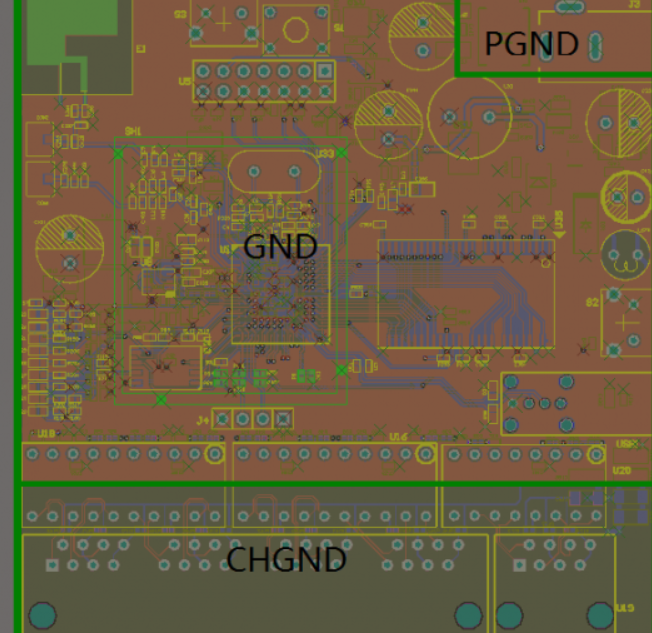

设置好铺铜要求后点击ok。这时候如图4所示,看到鼠标呈现出一个大十字光标。这时候你可以沿着keepout外框线画出一个铺铜的轮廓,画好轮廓后右击一下鼠标。这时候软件就开

2018-08-30 15:36

信号完整性要求,给高频数字信号一个完整的回流路径,并减少直流网络的布线。当然还有散热,特殊器件安装要求铺铜等等原因。

2018-05-04 17:03

铺铜的一大好处是降低地线阻抗(所谓抗干扰也有很大一部分是地线阻抗降低带来的)数字电路中存在大量尖峰脉冲电流,因此降低地线阻抗显得更有必要一些,普遍认为对于全由数字器件组成的电路应该大面积铺地,而对

2019-08-15 15:59

对DC/DC 电源的电感底部是否应该铺铜这个问题,工程师们常常意见分歧。一种观点认为,在电感下方铺铜会在接地面上产生涡流;涡流会影响功率电感的电感量并增加系统损耗,而接

2022-03-11 09:45

所谓覆铜,就是将PCB上闲置的空间作为基准面,然后用固体铜填充,这些铜区又称为灌铜。覆铜的意义在于,减小地线阻抗,提高抗

2023-03-02 09:53

版图设计,电感下面怎么处理?针对不同类的产品,处理的方式也有所不同,一直以来,都是有不同看法的。

2022-11-12 09:11

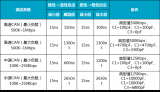

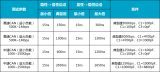

边沿时间分为上升沿时间、下降沿时间。下降沿时间是按照电压(20%~80%电压区间,有些按照10%~90%电压区间测量边沿时间,文中以20%~80%电压区间测量边沿时间)。表中给出时间范围,如果超出

2018-09-22 08:51

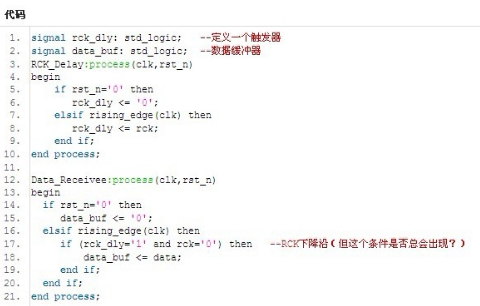

边沿触发器,指的是接收时钟脉冲CP 的某一约定跳变(正跳变或负跳变)来到时的输入数据。在CP=l 及CP=0 期间以及CP非约定跳变到来时,触发器不接收数据的触发器。具有下列特点的触发器称为边沿触发方式触发器,简称边沿

2018-01-31 09:02

在同步电路设计中,边沿检测是必不可少的!

2017-08-16 15:19

CAN总线边沿时间会影响采样正确性,而采样错误会造成错误帧不断出现,影响CAN总线通信。

2018-11-23 14:04