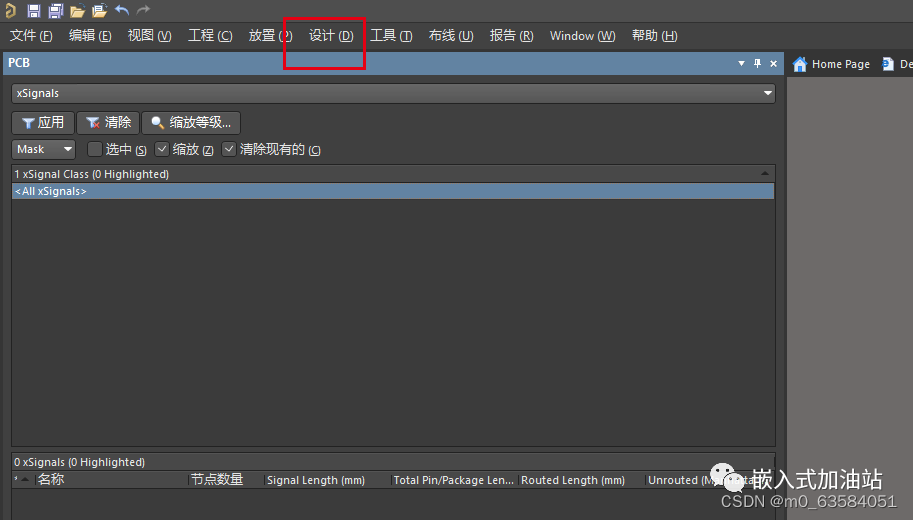

在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDR SDRAM)甚至 4 次,而随着芯片运行

2020-11-22 11:54

我们去PCB板厂转一圈,问他们:走线可以帮我们控10%的阻抗公差吗?他们会自信满满的答应你:没问题!如果你想再抠一下,控8%,他们会稍微考虑下,也拍板说:行(内层)!如果这时候你问:过孔能帮我控

2021-03-30 10:24

SDRAM有多种标准,包括DDR(Double Data Rate)、DDR2、DDR3和DDR4。每个标准都具有不同的物理规格和数据传输速率。DDR4是现代计算机中使用的最新型号,它具有更高的频率和更大的容量。

2023-08-26 11:57

很多人对于PCB走线的参考平面感到迷惑,经常有人问:对于内层走线,如果走线

2018-03-08 17:18

数字电路中,每个操作都需要在正确的时间执行,因为电子元件并不是瞬间完成其功能的。例如,在时钟信号的上升沿或下降沿处将数据写入存储器,然后等待一段时间后读取数据。如果在错误的时序下执行这些操作,从机数据接收错误,导致乱码,(奇偶校验位就是防止数据乱码)

2023-11-03 16:27

本文主要介绍了配电柜走线工艺及走线技巧。仔细查看工程施工通知上的有关说明,一次系统图上柜体结构,元件布置和材料明细表上元件型号以及对元件的要求。

2019-08-01 15:59

从原理上说,直角走线会使传输线的线宽发生变化,造成阻抗的不连续。其实不光是直角走线,顿角,锐角

2019-09-25 14:32

表层走线与内层走线更为规范的说法应该是微带线与带状线。两种

2020-12-19 10:23

其中W为走线宽度,l为走线长度,可以发现PCB走线电感与敷铜厚度无关,走线

2023-01-19 09:11

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中是至关重要的。下面将针对实际布线中可能遇到的一些情况,分析其合理性,并给出

2018-04-14 11:06