方法1.通过状态机来实现,通过verilog控制FPGA,让它该快的时候快,该慢的时候慢。

2023-11-02 09:48

本文首先介绍了verilog的概念和发展历史,其次介绍了verilog的特征与Verilog的逻辑门级描述,最后介绍了Verilog晶体管级描述与

2018-05-14 14:22

Verilog 提供了 2 大类时序控制方法:时延控制和事件控制。事件控制主要分为边沿触发事件

2023-06-02 11:44

在此利用Verilog HDL设计了一款CAN总线控制器,首先根据协议把整个CAN总线控制器划分为接口逻辑管理、寄存器逻辑和CAN核心模块3个模块,然后用Verilog

2012-07-31 14:25

Verilog HDL是一种用于数字系统设计的语言。用Verilog HDL描述的电路设计就是该电路的Verilog HDL模型也称为模块。Verilog HDL既是一

2019-03-08 14:29

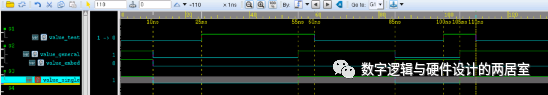

Verilog测试平台设计方法是Verilog FPGA开发中的重要环节,它用于验证Verilog设计的正确性和性能。以下是一个详细的Verilog测试平台设计方法及

2024-12-17 09:50

Verilog 与 VHDL 比较 1. 语法和风格 Verilog :Verilog 的语法更接近于 C 语言,对于有 C 语言背景的工程师来说,学习曲线较平缓。它支持结构化编程,代码更直观,易于

2024-12-17 09:44

的完整 Verilog 代码 。 在这个FPGA Verilog项目中,一些简单的处理操作都是在Verilog中实现的,比如反相、亮度控制和阈值操作。图像处理操作由“p

2021-09-23 15:50

,SDRAM的控制逻辑复杂,使用很不方便。 为了解决这个矛盾,需要设计专用的SDRAM控制器,使系统用户象使用SRAM一样方便的使用SDRAM是十分必要的。考虑到控制器的通用性,本文提出了一种通用的SDRAM

2021-06-30 09:16

Verilog与ASIC设计的关系 Verilog作为一种硬件描述语言(HDL),在ASIC设计中扮演着至关重要的角色。ASIC(Application Specific Integrated

2024-12-17 09:52