本文主要使用了Cadence公司的时域分析工具对DDR3设计进行量化分析,介绍了影响信号完整性的主要因素对DDR3进行时序分析,通过分析结果进行改进及优化设计,提升信号质量使其可靠性和安全性大大提高。##时序分析。##PCB

2014-07-24 11:11

不知道你有没有在画PCB呢,在画的时候,遇到了些什么问题呢?

2023-11-13 14:18

从那时起,采用DDR2、甚至最新的DDR3 SDRAM的新设计让DDR SDRAM技术黯然失色。DDR内存主要以IC或模块的形式出现。如今,

2011-07-11 11:17

突发长度,由于DDR3的预期为8bit,所以突发传输周期(BL,Burst Length)也固定位8,而对于DDR2和早期的DDR架构的系统,BL=4也是常用的,DDR3

2018-06-21 09:20

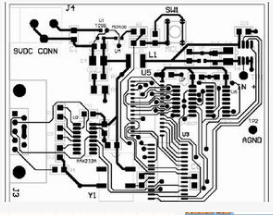

双层pcb板正反两面都有布线,元器件可以焊接在正面,也可以焊接在反面,双层线路板这种电路板的两面都有元器件和布线,不容质疑,设计双层PCB板的难度要高更多,下面我们来分析下双层pcb板布线规则并分享给大家如何

2017-08-26 16:03

本文章主要涉及到对DDR2和DDR3在设计印制线路板(PCB)时,考虑信号完整性和电源完整性的设计事项,这些是具有相当大的挑战性的。文章重点是讨论在尽可能少的PCB层数

2018-02-06 18:47

DDR3内存已经被广泛地使用,专业的PCB设计工程师会不可避免地会使用它来设计电路板。本文为您提出了一些关于DDR3信号正确扇出和走线的建议,这些建议同样也适用于高密度、紧凑型的电路板设计。

2018-06-16 07:17

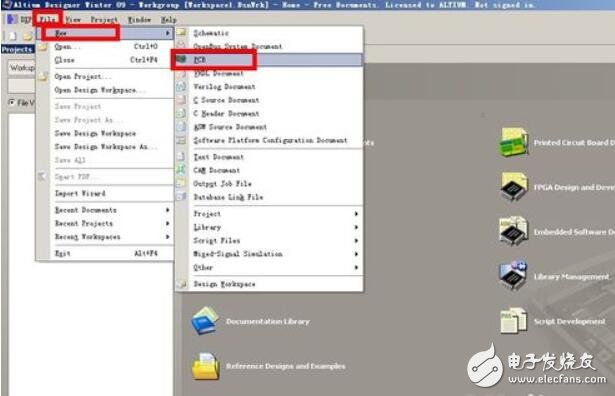

在使用Altium Designer 画PCB时,多数时候画双面板的比较多,但有时抗信号干扰要求更高的情况下,可能会设计四层板或者更多层板,下面以Altium Designer09软件为例,介绍如何

2019-05-17 14:42

我们通过Configuration,Package,Speed...等DDR3的命名可知道DDR3的容量,封装,速度等级等信息。

2019-03-03 11:04

有的元件在库里找不到是要自己画的,其实实际中还是自己画好,最后有一个自己的库,那才叫方便呢。画的过程是启动FILE/NEW——》选择SCH LIB——》这就进入了零件编辑库——》画完后在该元件上又键TOOLS—REN

2019-08-20 15:04