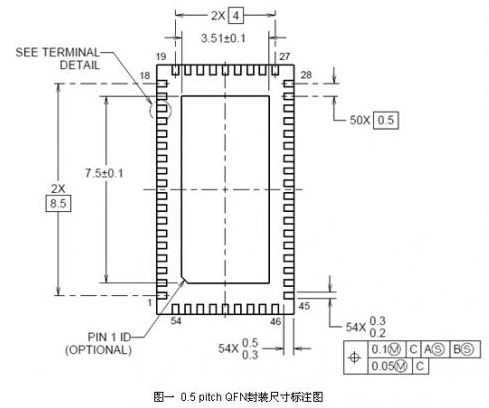

在PCB设计中,QFN封装的器件通常使用微带线从TOP或者BOTTOM层扇出。对于小间距的QFN封装,需要在扇出区域注意微带线之间的距离以及并行走线的长度。

2019-10-04 17:09

在PCB设计中,“间距”绝对是个绕不开的重要话题。

2025-04-15 16:18

AD封装转ALLEGRO封装时,要把所有封装放到一张PCB上或者分批次的放到PCB上,把

2018-04-05 17:06

比如覆铜间距16mil,其他安全间距8mil,过孔到过孔间距100mil,焊盘到过孔间距100mil,顶层地覆铜0.8mm,顶层VCC3.3与VCC1.8覆铜

2018-12-27 08:46

答:PCB封装就是把实际的电子元器件,芯片等的各种参数(比如元器件的大小,长宽,直插,贴片,焊盘的大小,管脚的长宽,管脚的间距等)用图形方式表现出来,以便可以在画pcb

2022-07-08 09:56

QFN封装的引脚间距较小是指在该封装中,相邻引脚之间的距离相对较小。这种设计有助于减小整体封装的尺寸,使芯片的集成更加紧凑,从而在有限的空间内容纳更多的引脚和电路。这也

2024-02-23 09:48

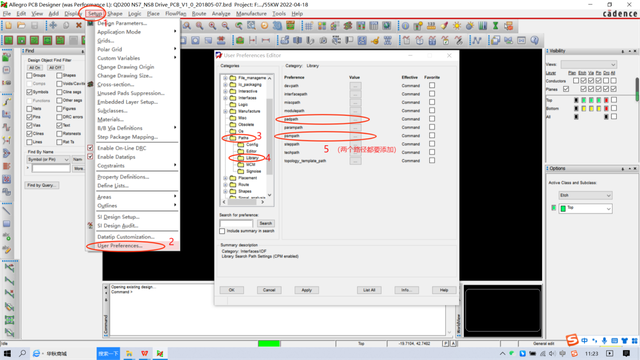

首先打开需要的PCB文件,点击setup→user preferences,在弹出的对话框中选择paths→library→padpath/psmpath(这两个路径都要添加上,否则从原理图导PCB的时候可能会报错)

2023-03-27 17:21

在PCB设计流程当中,一块PCB板完成了布局布线,又检查连通性和间距都没有报错的情况下,一块PCB是不是就完成了呢?

2017-04-19 10:19

W1.0mm。整个字符的高度H1.2mm。字符之间的间距D0.2mm。当文字小于以上标准时加工印刷出来会模糊不清。

2019-05-31 16:35

上面所描述的封装其实是一种常见封装,双列直插DIP-xx,其中xx代表引脚的数量,由于上面的芯片只有8个引脚,所以封装就是DIP-8,这是一种标准封装,引脚

2023-03-02 09:50