小间距QFN封装PCB设计串扰抑制分析

2022-11-04 09:51

一、引言随着电路设计高速高密的发展趋势,QFN封装已经有0.5mm pitch甚至更小pitch的应用。由小间距QFN封装的器件引入的PCB走线扇出区域的串扰问题也随着

2019-07-30 08:03

AD pcb设计规则检查报错Silk To Solder Mask Clearance Constraint报错原因处理方法一:改变规则中的最小间距:方法二:直接取消这

2021-12-04 15:21

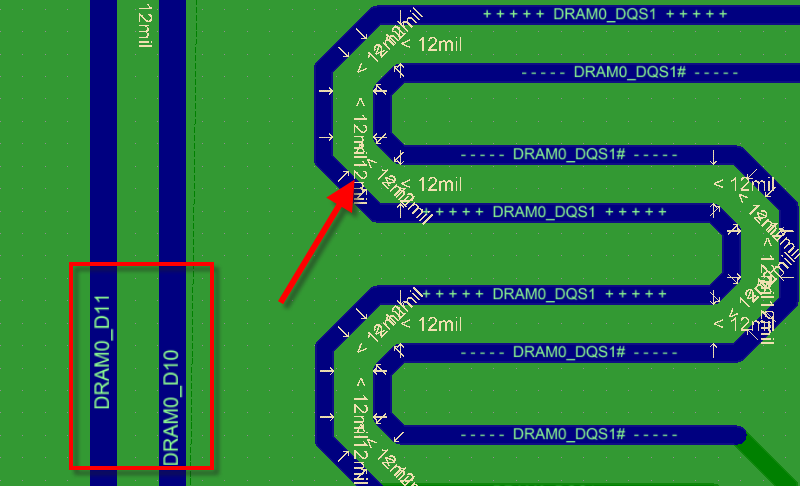

随着电路设计高速高密的发展趋势,QFN封装已经有0.5mm pitch甚至更小pitch的应用。由小间距QFN封装的器件引入的PCB走线扇出区域的串扰问题也随着传输速率

2021-03-01 11:45

的设置)也会DRC报错,产生很多DRC报告,难以分辨,如图12-23所示。 图12-23 DRC报告 如何解决这个问题呢?可以利用Altium Designer的高级规则编辑功能,对差分线进行过滤。 (1)按快捷键DR,进入PCB规则及约束编辑器,新建一个

2020-04-22 15:26

PCB设计中的间距是指电路板上元器件之间或导线之间的距离。小间距和微间距是两种不同的术语,它们在电路板设计中扮演着关键角色,但有着明显的区别。今天捷多邦小编就与大家好好

2024-05-21 17:52

pitch甚至更小pitch的应用。由小间距QFN封装的器件引入的PCB走线扇出区域的串扰问题也随着传输速率的升高而越来越突出。对于8Gbps及以上的高速应用更应该注意避免此类问题,为高速数字传输链路

2021-11-10 09:42

在将原理图通过网表导入或者直接导入的方式导入到PCB中,我们有时候可以看到同封装的焊盘在进行绿色报错,一般情况下是多管脚的IC元器件报错,例如可以看到如图5-15所示的

2020-09-21 15:22

一、引言随着电路设计高速高密的发展趋势,QFN封装已经有0.5mm pitch甚至更小pitch的应用。由小间距QFN封装的器件引入的PCB走线扇出区域的串扰问题也随着

2022-11-21 06:14

Altium关于nucleo板子中的pcb 0欧封装报错问题,请问怎么解决?

2024-05-10 06:55