首先将线宽不同的两块板(表层铺地前)由ALLEGRO导入SIWAVE,在目标线上加入50Ω端口。针对不同线宽0.1016mm和0.35mm, 我们的仿真结果如图2所示,图中显示的曲线是S21,仿真频率范围为800MHz-1GHz。

2019-09-17 14:42

时钟晶体下面铺地和走线

2023-11-24 15:37

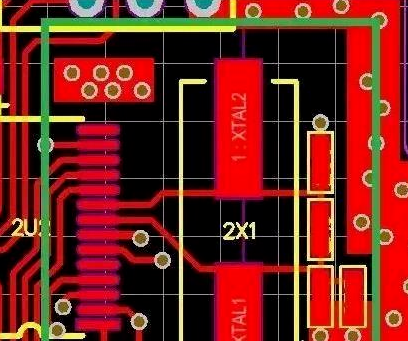

我们将对多层电路板进行射频线仿真,为了更好的做出对比,将仿真的PCB分为表层铺地前的和铺地后的两块板分别进行仿真对比;表层未铺地的PCB文件如下图1所示。

2018-04-09 15:54

在PCB时钟电路区域只布与时钟电路有关的器件,避免布设其他电路,晶体附近或者下面不要布其他信号线:在时钟发生电路、晶体下使用地平面,若其他信号穿过该平面,违反了映像平面功能,如果让信号穿越这个地平面的话

2024-01-11 15:43

静电问题是每个产品、单板都不能忽视的存在,那该如何解决ESD问题呢?向师傅请教,查找ESD标准,看ESD设计的相关书籍,逛技术论坛,看线上直播。..。..

2020-06-19 10:16

单板上时钟的注意事项,主要有以下几个方面可以考虑。

2023-05-09 10:09

单板上时钟的注意事项 单板上时钟晶体下面铺地的好处 单板上时钟是指将时钟晶体组件直接铺装在电路板上,这种设计方案在电子设备中广泛应用。在介绍单板上时钟的注意事项之前,让我们先了解一下为什么要在单板上

2024-02-06 16:06

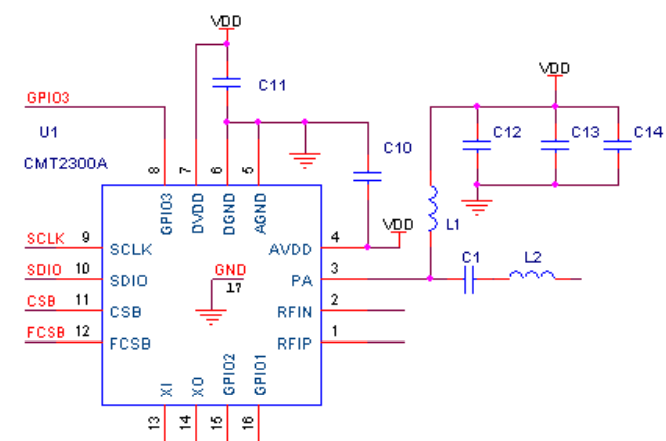

数字信号(包括串口和 GPIO 口)的走线注意事项如下: 1. 数字信号应尽量远离晶体和 RF 走线。 2. 数字信号应尽可能用地围起来,以减少相互串扰。 3. 在布线不合理或走线太长情况下,串口 CSB,FCSB,SDIO,SCLK 管脚容易受到干扰,功率输出(20dBm)越大,工作频率越低,受干扰的概率越大。

2019-09-21 11:50

1) 假如板边的屏蔽过孔可以与系统的接地螺柱连接有效(注意是有效的话,螺孔多,而且分布合理,这个比较抽象哦,展开讲又得几百字),泄放静电能力是没有问题,有没有效就得看静电是否存在这种直接灌入的条件啦(例如端口的连接器采用的是金属外壳,搭接就要求良好)。

2020-06-05 11:31

1. 当焊盘和大面积的地相连时,应优选十字铺地法和45°铺地法。 2.

2006-04-16 20:19