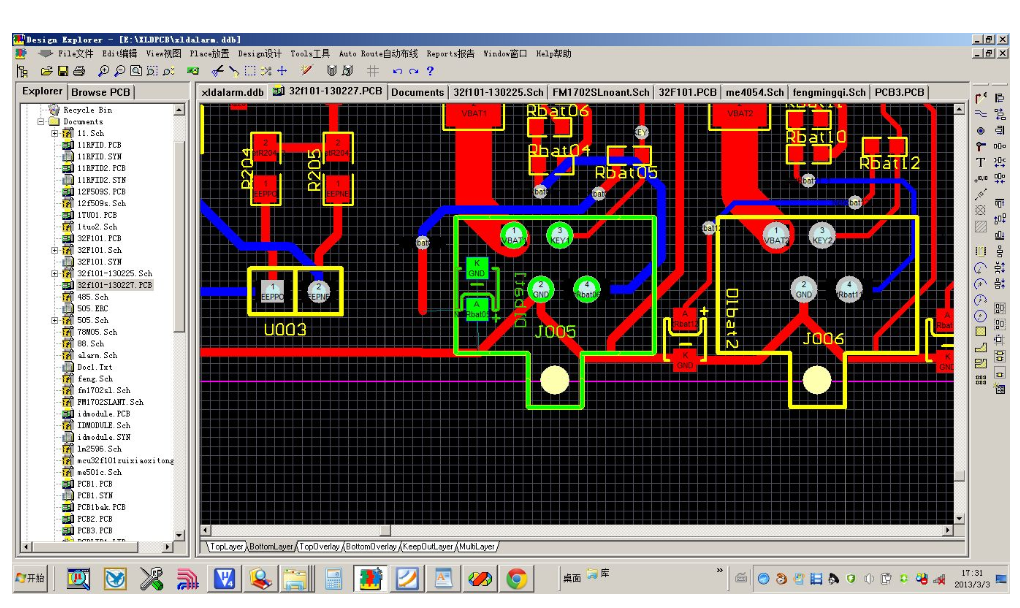

原理图常见错误1)ERC报告管脚没有接入信号:a. 创建封装时给管脚定义了I/O属性;b.创建元件或放置元件

2018-11-18 11:06

在使用单片机定时器进行计时设置的过程中,出现设置错误的情况是在所难免的,这就需要我们采取一些方法对已经造成的错误进行纠正了。由于单片机的机器周期通常为1μs~2μs

2020-06-25 18:46

1.原理图常见错误: (1)ERC报告管脚没有接入信号: a. 创建封装时给管脚定义了I/O属性; b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上; c. 创建元件时pin方向反向,必须非pin name端连线。

2019-09-11 14:14

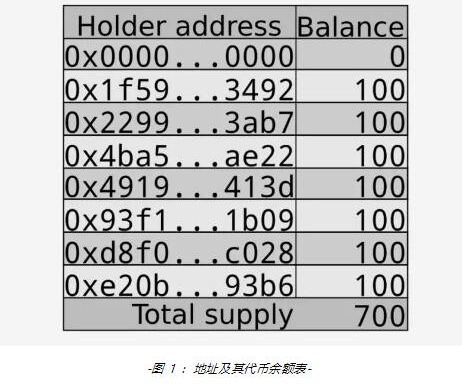

ERC-777是一种新的代币合约标准,解决了 ERC-20 的一些安全问题,可以让合约创建者、代币持有者和受众在无需更改代币合约的情况下扩展其功能。

2019-11-19 11:16

1.原理图常见错误: (1)ERC报告管脚没有接入信号: a. 创建封装时给管脚定义了I/O属性; b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上; c. 创建元件时pin方向反向,必须非pin na

2019-11-09 10:32

SUMIF函数是Excel中一个非常实用的函数,用于根据给定条件对数据进行求和。然而,在使用过程中,用户可能会遇到一些常见错误。 1. 错误:范围不正确 错误描述: 用户可能没有正确

2024-11-11 09:10

其中,最低5bits为当前错误指针(First Error Pointer),当相关错误状态更新时,该指针由硬件自动更新。一般情况下,当前错误指针指向的错误是优先级最高

2018-08-27 11:31

Xilinx Vivado开发环境编译HDL时,对时钟信号设置了编译规则,如果时钟由于硬件设计原因分配到了普通IO上,而非_SRCC或者_MRCC专用时钟管脚上时,编译器就会提示错误。

2024-04-15 11:38

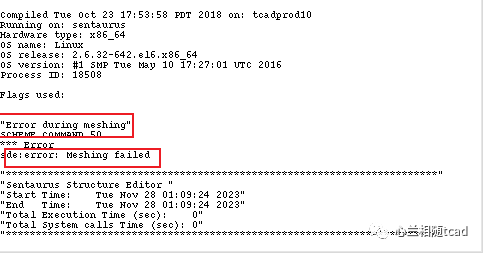

本推文针对Sentaurus初学者频繁遇到的错误进行简单整理,具体是包括Sde、Sdevice仿真常见错误。

2023-12-03 16:24