本文开始介绍了三态门的定义与三态门的应用,其次对三态门的三态及特点进行了介绍,最后阐述了三态输出门电路与

2018-03-01 14:47

三态数据缓冲器是数据输入/输出的通道,数据传输的方向取决于控制逻辑对三态门的控制。本文介绍三态缓冲器的逻辑符号。

2018-01-11 10:42

本文着重探讨 HDIO OBUFT 和 IOBUF 用例。如果含三态控制 (OBUFT/IOBUF) 的 HDIO 输出缓冲器的上电电压为 3.3 V 或 2.5 V 并且 Data(数据)控制信号与 Tristate(三态)控制信号的切换时间彼此相近,则可能会受

2023-07-12 09:50

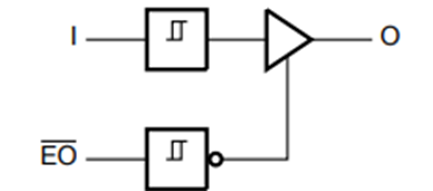

三态指其输出既可以是一般二值逻辑电路,即正常的高电平(逻辑1)或低电平(逻辑0),又可以保持特有的高阻抗状态。本文开始介绍了三态门的定义,其次介绍了三态门的逻辑符号,最后介绍了

2018-03-01 14:03

三态逻辑作为一种数字电子技术中的逻辑类型,允许信号线在三种状态之间切换。本文介绍了三态逻辑电路原理并介绍了四种基本类型的三态缓冲器。如果你对

2024-08-01 09:59

低电平,随它后面接的东西定。三态门,是指逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路。高阻态相当于隔断状态(电阻很大,相当于开路)。 三态门

2017-12-25 11:27

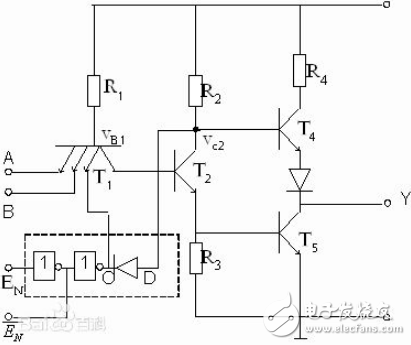

常规的硬件实验测试三态总线电路逻辑功能的方法是,将三态输出门的控制端、输入端分别接逻辑电平开关,改变逻辑电平开关为逻辑1、逻辑0观测输出函数的逻辑状态。存在的问题是,总线分时传输关系不直观。用

2020-04-18 12:50

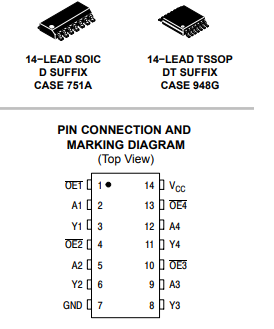

高速CMOS四总线缓冲器MC74VHC125DG带三态控制输入 EDA模型与数据手册分享

2025-05-29 15:02

本文主要介绍了传输门和三态门什么区别,三态门就是指输出有三种状态(0,1,高阻)的门。传输门就是指可以控制通路通断的门,导通时,一端的信号可以传到另一端,不导通时,一端信号不能传到另一端。两者不是

2018-04-08 15:33

大学计算机教学中的计算机硬件实验。在计算机硬件实验中,三态电路有着广泛的应用,例如构建一个具有分时共享功能的总线电路就需要用到多个三态电路。

2020-08-07 17:14