请教一下,multisim 14,画电路图的元件,元件如何对称放置,等距离放置,能否测出两个元件之间的距离,格数,以便图纸美观,均匀,谢谢! 补充内容 (2018-1-16 14:43): 不好意思,在手机上面没有找到multisim论坛,发错了地方,请管理员删

2018-01-16 12:17

请教一下,multisim 14,画电路图的元件,元件如何对称放置,等距离放置,能否测出两个元件之间的距离,格数,以便图纸美观,均匀,谢谢!

2018-01-16 14:46

PCB长距离走线和短距离加个过孔走线哪种

2019-09-25 22:11

时,一般需要保持DP/DN在走线的过程中保持等距,保证一定的耦合程度,但是需要弄清楚的时,等长的优先级是高于等距的。且在走

2018-05-21 11:53

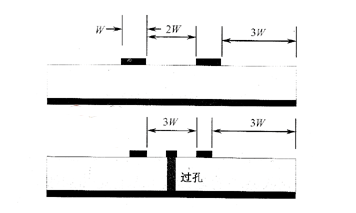

降低信号的质量,其机理可以参考对共模和差模串扰的分析。下面是给Layout工程师处理蛇形线时的几点建议:1、尽量增加平行线段的距离(S),至少大于3H,H指信号走线到参

2013-11-13 21:42

摘要详细介绍了最佳非等距插值算法在热敏电阻测系统中的应用,给出了实现仿真的计算公式和有效数据。这种算法的运用,可以简化计算,提高运算速度。相对于等距离线性插值

2009-01-17 13:18

3-W原则就是让所有的信号走线的间隔距离满足:走线边沿之间的距离应该大于

2023-08-29 14:39

的噪声和干扰,提高信号的完整性和可靠性。在设计和调整走线拓扑架构时,需要考虑信号线路的长度、走向、分布以及与其他线路之间的距离等因素。下面将详细介绍走

2023-11-24 14:44

规则一:高速信号走线屏蔽规则 如上图所示: 在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。 建议

2020-02-14 11:53

,为了保证信号有足够的保持时间,或者减小同组信号之间的时间偏移,往往不得不故意进行绕线。 那么,蛇形线对信号传输有什么影响呢?走线时要注意些什么呢?其中最关键的两个参数就是平行耦合长度(Lp)和耦合

2012-12-18 12:12