分享一个Congestion的示例与解决这个Congestion用的2种方法以及对应的效果。

2023-01-31 17:17

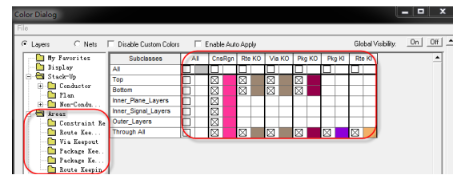

就在Areas,如图5-60所示。 图5-60 各类布局布线区域示意图 在Allegro软件中有Route Keepout、Route Keepin、Package Keepout、Package

2020-10-13 11:12

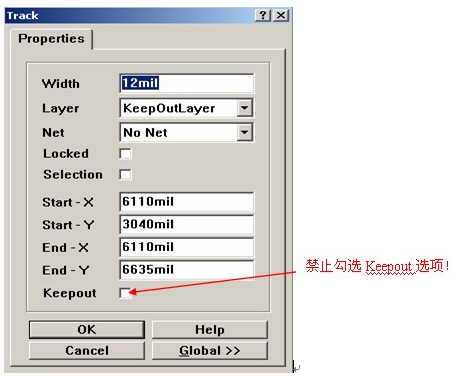

Protel系列、AD系列软件所画的线,不论画在哪一层(包括走线层、Keepout层等),双击打开线的属性,一定不能勾选keepout选项,一旦选中了keepout选项,则这根线无法在gerber文件中生成,导致此线

2019-10-23 14:32

设置好铺铜要求后点击ok。这时候如图4所示,看到鼠标呈现出一个大十字光标。这时候你可以沿着keepout外框线画出一个铺铜的轮廓,画好轮廓后右击一下鼠标。这时候软件就开始铺铜工作,稍等一下就可以看到铺铜效果了。比如图5,我粗糙的铺铜后。

2018-08-30 15:36

Altium Designer为例来说明。 在PCB设计中用得比较多的图层 mechanical 机械层 keepout layer 禁止布线层 Signal layer 信号层 Internal

2020-08-17 11:25

认识到提高设计正确性,通过使项目设计一次成功,来减少返工时间,从而提升设计效率达到缩短项目周期的目的。 以往我们使用allegro 16X设计时,遵循DXF约束布局时我们通过设置合理的PACKAGE KEEPIN、 PACKAGE KEEPOUT和ROUTE KEEPIN等规则,结合合理

2021-03-29 11:59

的铜时的边界,也就是说我们先定义了禁止布线层后,我们在以后的布过程中,所布的具有电气特性的线是不可能超出禁止布线层的边界,常常有些习惯性把Keepout层作为机械层来使用,这种方式其实是不对的,所以建议大家进行区分,不然每次生产的时候板厂都要给你进行属性变更。

2018-08-31 17:34

10mil线画板框(部分工程师喜欢用禁止布线层即KeepOut-Layer层)P+L布线。 4、在布置PCB时,必须先要设置规则(很重要),rule中要设置Via、Clearance等。放置元件,过孔,焊

2020-11-16 14:46

、画完后要规定禁止布线层即 KeepOut-Layer 层,P+L 布线 5、覆铜(place polygon pour)之前要修改安全间距 design rules(clearance 16mil

2020-10-30 15:41

有效减少焊盘的分布电容,从而维持信号传输的阻抗一致性,这种设计优化在射频电路中尤为重要。 利用FanySkill中的“布线功能-焊盘隔层挖空”选项,可以迅速为同一网络的焊盘在相邻层创建与焊盘尺寸相匹配的route keepout区域,即实现焊

2025-06-06 11:47