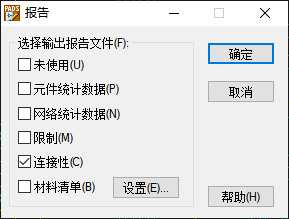

PROTEL原理图常见错误 (1)ERC报告管脚没有接入信号: a. 创建封装时给管脚定义了I/O属性; b

2010-03-15 10:22

在设计完并绘制完成原理图之后,就相当于完成大部分的工作了,但是还差最后一步,就是对于原理图的检查,就跟考试一样,做完试题之后,有效的检查可以减少犯

2023-11-07 10:48

在嵌入式应用中,有可能发生各种各样的错误,系统必须能够检测到这些错误并作出适当的响应。RTOS通常内置了一些错误检查功能,用于检测

2025-01-03 14:44

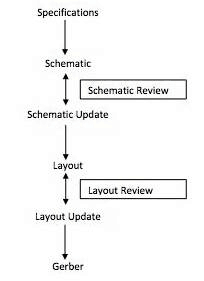

在电子设计领域,原理图和PCB设计是产品开发的基石,但设计过程中难免遇到各种问题,若不及时排查可能影响电路板的性能及可靠性,本文将列出原理图和PCB设计中的常见错误,整理成一份实用的速查清单,以供参考。

2025-05-15 14:34

1.原理图常见错误: (1)ERC报告管脚没有接入信号: a. 创建封装时给管脚定义了I/O属性; b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上; c. 创建元件时pin方向反向,必须非pin name端连线。

2019-09-11 14:14

Altium有时候总是显示DRC错误,不知道哪里出了问题,下面小编带大家学习一下常见的DRC检查有哪些?

2018-09-23 12:27

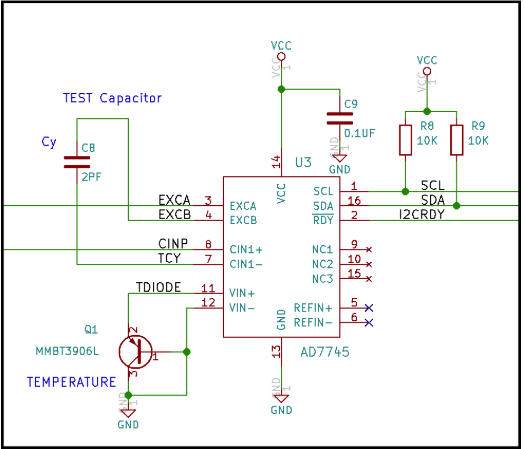

无差错原理图的基础是精确的符号。精通原理图捕获软件中的符号编辑器非常重要。

2019-09-18 08:34

在原理图设计过程中可能会产生100多个错误,您能在审查过程中全部发现吗?来看看如何把它们一网打尽吧。

2018-06-11 09:17

如何检查PCB与原理图的网络表是否一致 首先说明我用orcad做原理图,powerpcb 做pcb,但思路你可以借鉴用最新的原理图生成powerpcb的网表文件,打开

2008-03-22 18:16

为了避免错误,应该有一种方法可以在几秒钟内检查完整的原理图。该方法可以通过原理图仿真实现,这在当前的电路板设计流程中很少见。原理

2019-07-31 10:04