在项目中曾经把一个芯片的2个引脚画反了,导致最后制版出来后不得不跳线,这样就很难看了。 所以,检查与原理图前一定要从芯片的封装入手,坚决把错误的封装扼杀在摇篮中!2. 使用protel

2019-07-04 09:20

altium designer 为什么不检查原理图电气错误。。。明明有两个电阻同名可是就是不报告错误的,,我没有放大叉。。。。就是不

2012-09-12 16:27

在使用cadence设计原理图时,有时会出现一些连线错误,如单网络,信号互连错误等等,业界有没有专业的针对cadence的检查工具,能够设置一些条件,将

2015-02-09 15:58

本帖最后由 gk320830 于 2015-3-9 22:48 编辑 Pads2005原理图设计是怎样检查错误?[此贴子已经被电子发烧友于2009-3-31 14:02:25编辑过]

2009-03-27 00:02

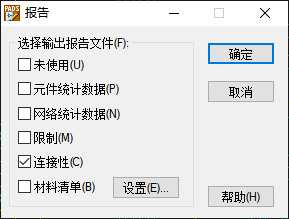

本帖最后由 郑振宇altium 于 2019-11-19 14:43 编辑 我们在设计完原理图后到设计PCB之前,我们可以利用软件自带的ERC功能对一些常规的电气性能进行检查,可以去避免一些

2019-11-19 14:41

芯片的2个引脚画反了,导致最后制版出来后不得不跳线,这样就很难看了。所以,检查与原理图前一定要从芯片的封装入手,坚决把错误的封装扼杀在摇篮中!2. 使用protel的Tools->ERC电气规则

2014-06-05 15:09

电气规则检查,DXP应该也会有相应的菜单可以完成这样一个检查。很有用,它可以帮你查找出很多错误,根据它生成的错误文件,对照着错误

2018-08-15 10:11

PROTEL原理图常见错误 (1)ERC报告管脚没有接入信号: a. 创建封装时给管脚定义了I/O属性; b

2010-03-15 10:22

在设计完并绘制完成原理图之后,就相当于完成大部分的工作了,但是还差最后一步,就是对于原理图的检查,就跟考试一样,做完试题之后,有效的检查可以减少犯

2023-11-07 10:48

在嵌入式应用中,有可能发生各种各样的错误,系统必须能够检测到这些错误并作出适当的响应。RTOS通常内置了一些错误检查功能,用于检测

2025-01-03 14:44