在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDR SDRAM)甚至 4 次,而随着芯片运行

2020-11-22 11:54

本文主要介绍的是pcb开窗,首先介绍了PCB设计中的开窗和亮铜,其次介绍了如何实现PCB走线开窗上锡,最后阐述了PCB设计怎样设置

2018-05-04 15:37

在DDR的设计中,需要对数据线及地址线进行分组及等长来满足时序匹配,通常DDR的数据线之间的长度误差需要保证在50mil以内,地址

2022-11-02 09:25

SDRAM有多种标准,包括DDR(Double Data Rate)、DDR2、DDR3和DDR4。每个标准都具有不同的物理规格和数据传输速率。DDR4是现代计算机中使用的最新型号,它具有更高的频率和更大的容量。

2023-08-26 11:57

在当前的PCB 设计当中,对于走线长度的要求越来越多。Expedition PCB 自动调线的功能强大。在PCB 的设计当中若能最大限度地使用Expedition PCB 的自动调线功能,将有利于提高设计效率,特别是

2018-05-15 10:49

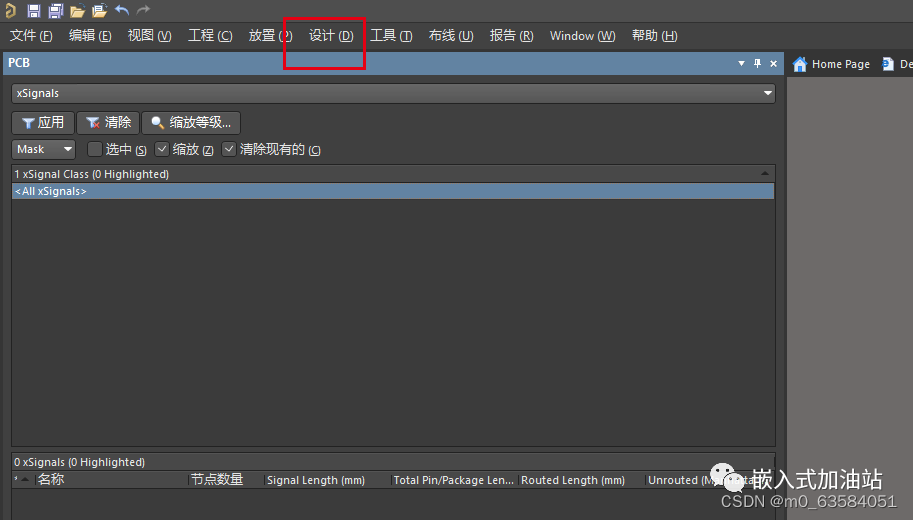

本例中需要实现PCI-e金手指到EMMC芯片等长,包括D0-D7,CLK,CMD这10条网络。查看各条网络,确认是否存在串联匹配电阻。本例中,仅在时钟线上存在,如下图的高亮器件。

2019-06-22 09:44

很多人对于PCB走线的参考平面感到迷惑,经常有人问:对于内层走线,如果走线

2018-03-08 17:18

数字电路中,每个操作都需要在正确的时间执行,因为电子元件并不是瞬间完成其功能的。例如,在时钟信号的上升沿或下降沿处将数据写入存储器,然后等待一段时间后读取数据。如果在错误的时序下执行这些操作,从机数据接收错误,导致乱码,(奇偶校验位就是防止数据乱码)

2023-11-03 16:27

在PCB设计中,走线命令是频繁使用的功能之一。执行走线命令后,通常会在Options面板中显示线宽、层、角度等设置选项,用于调整

2025-06-05 09:30

本文主要介绍了配电柜走线工艺及走线技巧。仔细查看工程施工通知上的有关说明,一次系统图上柜体结构,元件布置和材料明细表上元件型号以及对元件的要求。

2019-08-01 15:59