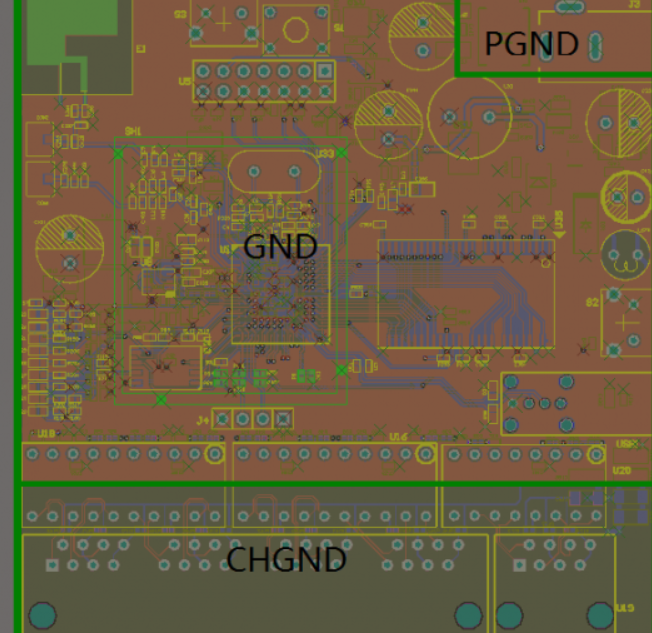

我们将对多层电路板进行射频线仿真,为了更好的做出对比,将仿真的PCB分为表层铺地前的和铺地后的两块板分别进行仿真对比;表层未铺地的PCB文件如下图1所示。

2018-04-09 15:54

首先将线宽不同的两块板(表层铺地前)由ALLEGRO导入SIWAVE,在目标线上加入50Ω端口。针对不同线宽0.1016mm和0.35mm, 我们的仿真结果如图2所示,图中显示的曲线是S21,仿真频率范围为800MHz-1GHz。

2019-09-17 14:42

铺铜的一大好处是降低地线阻抗(所谓抗干扰也有很大一部分是地线阻抗降低带来的)数字电路中存在大量尖峰脉冲电流,因此降低地线阻抗显得更有必要一些,普遍认为对于全由数字器件组成的电路应该大面积铺地,而对

2019-08-15 15:59

信号完整性要求,给高频数字信号一个完整的回流路径,并减少直流网络的布线。当然还有散热,特殊器件安装要求铺铜等等原因。

2018-05-04 17:03

设置好铺铜要求后点击ok。这时候如图4所示,看到鼠标呈现出一个大十字光标。这时候你可以沿着keepout外框线画出一个铺铜的轮廓,画好轮廓后右击一下鼠标。这时候软件就开始铺铜工作,稍等一下就可以看到

2018-08-30 15:36

对DC/DC 电源的电感底部是否应该铺铜这个问题,工程师们常常意见分歧。一种观点认为,在电感下方铺铜会在接地面上产生涡流;涡流会影响功率电感的电感量并增加系统损耗,而接地面噪声会影响其他高速信号。

2022-03-11 09:45

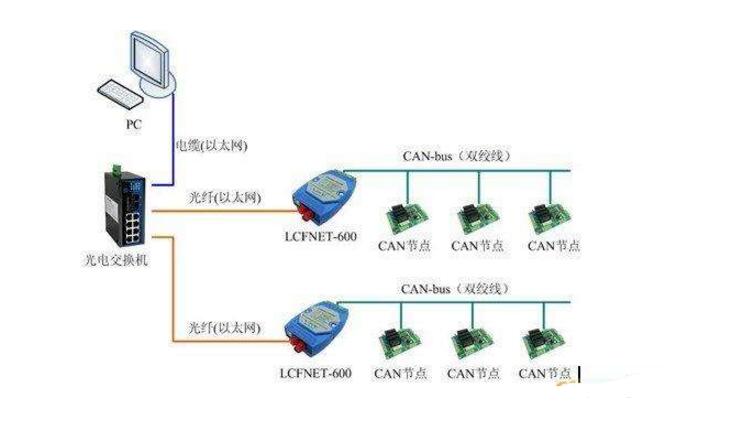

本文首先介绍了can总线的概念与特点,其次介绍了CAN总线原理与CAN总线的应用,最后分析了can总线是数字信号还是模拟信号以及阐述了模拟信号和数字

2018-04-25 09:15

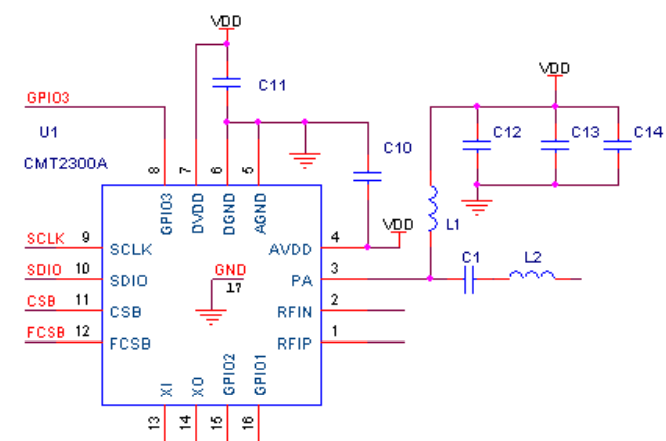

数字信号(包括串口和 GPIO 口)的走线注意事项如下: 1. 数字信号应尽量远离晶体和 RF 走线。 2. 数字信号应尽可能用地围起来,以减少相互串扰。 3. 在布线不合理或走线太长

2019-09-21 11:50

FPGA和CPU一直是雷达信号处理不可分割的组成部分。传统上FPGA用于前端处理,CPU用于后端处理。随着雷达系统的处理能力越来越强,越来越复杂,对信息处理的需求也急剧增长。为此,FPGA不断在提高

2022-12-14 11:46

CMOS电平是数字信号,COMS电路的供电电压VDD范围比较广在+5--+15V均能正常工作,电压波动允许±10,当输出电压高于VDD-0.5V时为逻辑1,输出电压低于VSS+0.5V(VSS为数字地)为逻辑0.

2017-08-26 17:26