在使用 Altium Designer 进行PCB设计时,除了电气间距(Clearance)等基础规则外, 导线宽度、阻焊层、内电层连接、铜皮敷设等规则也同样重要 。这些设置不仅影响布线效率,还决定了成品板的可制造性与可靠性。

2025-04-17 13:54

一个(如果不是这样的话),确保板元件之间足够间隙的主要原因是: 阻焊剂。这是一项基本的制造任务,可以保护您的电路板并帮助隔离必须在焊接过程中焊接的电气连接。印刷电路板。PCB设计步骤5:尽可能避免

2020-10-27 15:25

决嵌入式培训开发中的PCB设计问题。 嵌入式培训开发中PCB的输配电系统软件(PDS)设计方案能够忽视吗?这一每日任务常轻视,但针对系统软件级仿真模拟和数字设计工作人

2021-11-03 20:06

决嵌入式培训开发中的PCB设计问题。 嵌入式培训开发中PCB的输配电系统软件(PDS)设计方案能够忽视吗?这一每日任务常轻视,但针对系统软件级仿真模拟和数字设计工作人

2021-11-09 09:14

在成为工程师之前,我花了很多时间尝试开发其他人设计的产品。其中包括汽车,电器和电子设备。维修工作中最令人沮丧的事情是例行工作或预防性维护任务极为复杂或难以执行时。通常必须要做的事情最容易实现和执行。如果不是这种情况,很明显,设计师几乎没有考虑到某人将来必须执行这些所谓的例行任务这一事实。这种 监督的后果可能是巨大的,并导致停机时间过多,产量减少以及收入损失。 甚至比不考虑常规维护和维修更为严峻的是,在

2020-10-09 21:20

2013-03-05 22:07

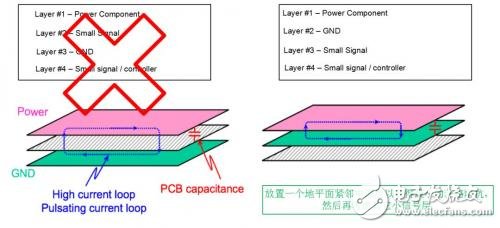

DC-DC的电路比LDO会复杂很多,噪声也更大,布局和layout要求更高,layout的好坏直接影响DC-DC的性能,所以了解DC-DC的layout至关重要。 1. Bad layoutEMI,DC-DC的SW管脚上面会有较高的dv/dt, 比较高的dv/dt会引起比较大的EMI干扰; 地线噪声,地走线不好,会在地线上面会产生比较大的开关噪声,而这些噪声会影响到其它部分的电路; 布线上产生电压降,走线太长,会使走线上产生压降,而降低整个DC-DC的效率; 2. 一般原则开关大电流回路尽量短; 信号地和大电流

2021-09-13 14:38

在系统设计布局规划上,电源电路应该尽可能靠近负载电路

2019-02-17 09:48

在查找、放置元件至PCB的过程中,交叉选择元件布局可以帮您节省时间。您有没有这样的经历?浪费了很多时间去查找电路板上的某个元件,最后发现,它藏在您原理图设计中另一个完全不同的位置上?交叉选择元件布局

2019-07-28 09:00

如输入/输出,交流/直流,强/弱信号,高频/低频,高压/低压等。..。 它们的走向应该是呈线形的(或分离),不得相互交融。其目的是防止相互干扰。最好的走向是按直线,但一般不易实现,最不利的走向是环形,所幸的是可以设隔离带来改善。对于是直流,小信号,低电压PCB设计的要求可以低些。所以“合理”是相对的。

2019-04-25 14:50