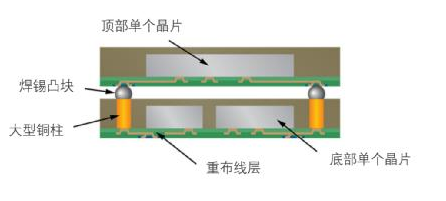

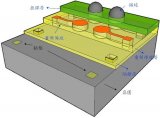

扇出型封装一般是指,晶圆级/面板级封装情境下,封装面积与die不一样,且不需要基板的封装,也就是我们常说的FOWLP/FOPLP。扇出型封装的核心要素就是芯片上的RDL重布线层(可参考下面图表说明

2023-11-27 16:02

本文主要介绍了SIMULINK示波器参数设置以及matlab中对示波器进行设置方法步骤。在SIMULINK中,示波器常用来作为输出工具,将模型的运行结果展现在人们面前。

2018-01-14 16:40

Fanout,即扇出,指模块直接调用的下级模块的个数,如果这个数值过大的话,在FPGA直接表现为net delay较大,不利于时序收敛。因此,在写代码时应尽量避免高扇出的情况。但是,在某些特殊情况下,受到整体结构设计的需要或者无法修改代码的限制,则需要通过其它优化

2019-10-13 14:55

Xilinx推荐对于低扇出的触发器控制信号在代码编写时尽量吸收进触发器D输入端之前的LUT中,并在XST的综合属性选项中提供配置项,让XST综合时自动将低扇出的控制信号吸收进触发器D输入端之前的LUT

2023-12-14 15:04

高密度扇出型封装技术满足了移动手机封装的外形尺寸与性能要求,因此获得了技术界的广泛关注。

2020-07-13 15:03

RDL 技术是先进封装异质集成的基础,广泛应用扇出封装、扇出基板上芯片、扇出层叠封装、硅光子学和 2.5D/3D 集成方法,实现了更小、更快和更高效的芯片设计。

2024-03-01 13:59

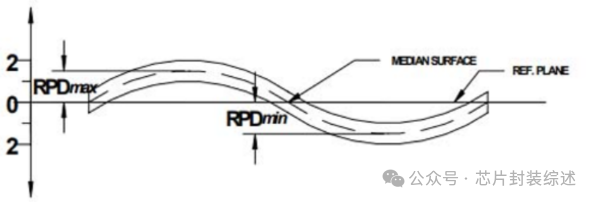

翘曲(Warpage)是结构固有的缺陷之一。晶圆级扇出封装(FOWLP)工艺过程中,由于硅芯片需通过环氧树脂(EMC)进行模塑重构成为新的晶圆,使其新的晶圆变成非均质材料,不同材料间的热膨胀和收缩程度不平衡则非常容易使重构晶圆发生翘曲。

2025-05-14 11:02

在PCB设计中如何设置格点的方法 合理的使用格点系统,能使我们在PCB设计中起到事半功倍的作用。但何谓合理呢?

2018-07-08 05:33

本文主要介绍了python程序调试中设置条件断点。实际开发中,调试代码通常要花费比新编写代码更多的时间,选择合理的调试方法和工具对于程序工作者来说很重要,一种更便捷更直观的方式就是使用断点调试。下文对此做了具体的分析

2018-01-14 11:39

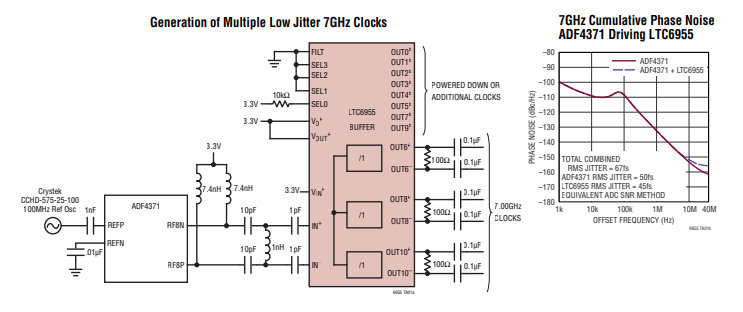

LTC6955 是一款具有十一个输出的高性能超低抖动扇出时钟缓冲器。它的 4 引脚并行控制端口允许多种输出设置(3 个和 11 个之间的任意个输出)以及完全关断。利用该并行端口还能够反转交流输出的输出极性,从而简化采用顶部和底部板布线的设计。

2025-04-09 15:19