复旦大学某ASIC实验室研究生新生FPGA基本知识入门培训。 主讲AXI-GP和AXI-HP总线的快速实现方式。 AXI-GP的Slave模块由我提供的脚本生成,里面的寄存器可以被ARM访问。 AXI-HP由我提供的AXI-HP转FIFO模块实现。需要给这个模块提供控制信号: 即从哪读,读多少个到FIFO中; 从FIFO中读多少个数,并写往哪里。

2019-08-06 06:15

经过这几年的市场磨砺,Zynq-7000 FPGA SoC器件平台在开发者中的认知度和接受度越来越高,这种“ARM处理器+可编程逻辑”的创新架构,可以帮助开发者在设计中找到高性能与灵活性的完美平衡,对此大家也心知肚明。 但是在实际的应用中,想要玩转

2018-06-26 06:40

基于Zynq的 FPGA芯片的动态智能家居系统:该系统采用智能小车作为移动网关,Zigbee作网络节点,用Sim300 GSM模块来实现短信收发功能.远程用户能够实时获取家里的信息。

2017-11-17 16:02

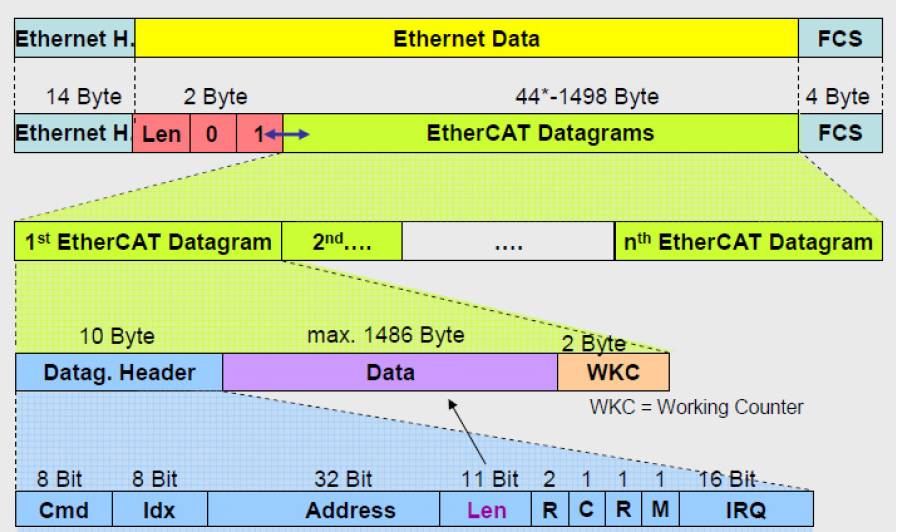

EtherCAT 是开放的实时以太网通讯协议,由德国倍福自动化有限公司研发。EtherCAT 具有高性能、低成本、容易使用等特点,目前在工业自动化领域有着广泛的应用。Zynq-7000是赛灵思公司

2017-11-16 14:02

本文最初发表在CSDN我的博客上,但是最近csdn博客管理不知道为何一直打不开,写不了新文章,干脆把博客搬到这边来。 这是玩米尔开发板遇到第一个问题,在此记录分享下。2019-10-27 使用jtag下载自己生产的boot_myir.bin成功,串口能够打印。怀疑可能用SD卡的那种方式传递boot不可靠,具体原因不详。下次的实验可以将uboot的IP地址更换,看看是否生效。Uboot更换ip生效。2019-11-14 烧写内核后产生错误如下:SF: 4718592 bytes @ 0x500000 Read: OKSF: 65536 bytes @ 0x800000 Read: OKCopying ramdisk...SF: 6291456 bytes @ 0x820000 Read: OKWrong Image Format for bootm commandERROR: can't get kernel image!不管使用项目的内核还是米尔的内核都是这个问题;有几个方向进行检查,首先看uboot中加载地址是否修改正确。其次修改设备树中烧写的地址。发现一个重要问题,用TFTP的方式无法成功烧写bin文件。同理如果这个问题不能解决,也说明可能用TFTP烧写的dtb,内核文件也是不成功的。重点解决。找到问题所在可能是TFTP传递地址过高导致,使用0x200 0000 和0x100 0000都不能正确烧写,传递到DDR3的0x8000地址即可正确烧写。具体原因待分析(可以通过查看硬件DDR3实际连接图对比看看)。不过也可以解释为何内核文件不正确。## Booting kernel from Legacy Image at 02080000 ...Image Name:Linux-3.15.0-xilinxImage Type:ARM Linux Kernel Image (uncompressed)Data Size: 3886088 Bytes = 3.7 MiBLoad Address: 00008000Entry Point:00008000Verifying Checksum ... Bad Data CRCERROR: can't get kernel image!然后再使用0x8000地址烧写后,内核应该是可以起来部分,应该是长度小了导致加载不完全使得CRC校验错误。将uboot的image的size改成0x400000然后将设备树和文件系统的起始地址后移到0x900000.然后不再报内核错误。只要这四个文件正确的写到相应的地址,且文件大小在uboot中设置正确,就不会再有内核或者文件系统不正常加载的问题。总结:1、在uboot的源码中设置好针对qspi启动的地址。2、要确认TFTP是否成功,尤其缓存地址如果太大,会出现烧写不成功的现象。这个在JTAG烧写就可以对比出来。疑问待解决:1、为何之前项目使用缓存地址0x200 0000可以正常TFTP烧写,而现在只能使用0x8000的缓存地址;2、看项目的uimag也差不多4M字节大小,而项目的uboot的地址分配给uimage只有0x300000的大小,却也可以正常启动。————————————————版权声明:本文为CSDN博主「buck_wan」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接及本声明。原文链接:https://blog.csdn.net/buck_wan/article/details/103087603

2020-03-09 16:13

Zynq平台运行SDK程序错误的解决办法,具体的跟随小编一起来了解一下。

2018-07-14 06:05

想把鸿蒙系统移植到zynq7000和zynqMP平台上,网上没有找到一点资料,对于一直一头雾水,不知道怎么入手。请问大家,有做过移植吗?

2022-10-20 17:02

本文介绍了在AMD Xilinx Zynq平台上实现嵌入式软件和FPGA设计的集成工作流程,使用Simulink进行Zynq模型设计,以及使用HDL协同仿真和FPGA-in-Loop进行集成硬件

2023-08-21 09:46

实验平台包括三个组成部分:待测试的EtherCAT系统、实时数据获取单元和离线的实验数据分析单元,如下图所示。主站为构建的嵌入式实时EtherCAT 主站,从站为两套松下交流伺服驱动器MADHT系列。

2019-07-30 09:45

,下面我们具体了解一下如何在Vivado平台中使用SmallRTOS操作系统。 在文件夹SmallRTOS_Zynq_Vivado_v1.00a下,按照路径\sw\repo\bsp找到SmallRTOS提供的bsp文件smallrtos_

2017-02-09 05:07