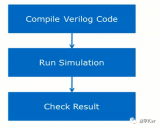

VCS是编译型verilog仿真器,VCS先将verilog/systemverilog文件转化为C文件,在linux下编译生成的可执行文./simv即可得到仿真结果。

2023-10-25 17:22

在linux系统上实现vivado调用VCS仿真教程 作用:vivado调用VCS仿真可以加快工程的仿真和调试,提高效率。 前期准备:确认安装vivado软件和VCS软件 VC

2018-07-05 03:30

几乎所有的芯片设计、芯片验证工程师,每天都在和VCS打交道,但是由于验证环境的统一化管理,一般将不同的编译仿真选项集成在一个文件里,只需要一两个人维护即可。所以大部分人比较少有机会去深入地学习VCS的仿真flow。基于此,本文将介绍

2023-01-10 11:20

VCS的仿真选项分编译(compile-time)选项和运行(run-time)选项。编译选项用于RTL/TB的编译,一遍是编译了就定了,不能在仿真中更改其特性,例如define等等。

2024-01-06 10:19

本篇文章来源于微信群中的网友,分享下在SpinalHDL里如何丝滑的运行VCS跑Vivado相关仿真。自此仿真设计一体化不是问题。

2022-08-10 09:15

VCS是一款常见的Verilog编译工具,它提供很多编译选项来控制编译过程及其输出。本文主要介绍以下两个编译选项。

2023-05-29 14:46

若想用Verdi观察波形,需要在仿真时生成fsdb文件,而fsdb在vcs或者modelsim中的生成是通过两个系统调用$fsdbDumpfile $fsdbDumpvars来实现的。

2020-09-22 15:01

由于vcs2014只支持gcc4.4的版本,而ubuntu16.4的gcc是5.4,所以需要先把gcc的版本降到4.4。

2018-12-02 09:23

前年,发表了一篇文章《VCS独立仿真Vivado IP核的一些方法总结》(链接在参考资料1),里面简单讲述了使用VCS仿真Vivado IP核时遇到的一些问题及解决方案,发表之后经过一年多操作上也有些许改进,所以写这篇文章补充下。

2022-08-29 14:41

VCS是编译型verilog仿真器,VCS先将verilog/systemverilog文件转化为C文件,在linux下编译生成的可执行文./simv即可得到仿真结果。

2022-05-23 16:04