本文介绍如何一步一步将设计从SDSoC/Vivado HLS迁移到

2021-01-31 08:12

本文介绍如何一步一步将设计从SDSoC/Vivado HLS迁移到

2022-07-25 17:45

。HLS 采用 C 和 C++ 描述并将它们转换为自定义硬件 IP,完成后我们就可以在 Vivado 项目中使用该IP。Vitis HLS创建一个新的

2022-09-09 16:45

Vitis Vision库是OpenCV和Vision功能的加速库,可在Vitis环境中使用,这些库的L1目录是示例设计。为了适应各种用户环境,从2020.1版本开始,

2022-02-16 16:21

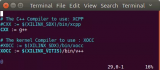

Vitis 2019.2 使用 gcc 编译 C 语言源代码,使用 Vivado HLS 编译与 SDAccel 流匹配的加速内核。此外,Vitis 也使用与 SDAc

2020-06-28 10:05

Vitis HLS 是一种高层次综合工具,支持将 C、C++ 和 OpenCL 函数硬连线到器件逻辑互连结构和 RAM/DSP 块上。Vitis

2022-05-25 09:43

对于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS

2022-09-02 09:06

Vitis HLS下,一个Solution的Flow Target可以是Vivado IP Flow Target,也可以是VitisKernel Flow Target,如下图所示。前者最终导出来

2020-11-05 17:43

,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到

2022-09-07 15:21

AMD Vitis HLS 工具允许用户通过将 C/C++ 函数综合成 RTL,轻松创建复杂的 FPGA 算法。Vitis HLS 工具与

2023-04-23 10:41