在Xilinx的Virtex6 FPGA中,GTX作为一种低功耗的吉比特收发器,配置灵活,功能强大,并与FPGA内部的其他逻辑资源紧密联系,可用于实现多种高速接口(如X

2017-02-11 05:11

PMP9475 12V 输入参考设计以紧凑高效的设计提供为 Xilinx's Virtex? Ultrascale? 系列 FPGA 供电时所需的所有电源轨。此设计使用几个 TI 的 PMBus 负载点电压稳压器以简化临界轨的设计/配置和遥测。

2017-02-16 17:50

Genesys Virtex-5 FPGA开发板集成了功能强大的Xilinx Virtex®-5 FPGA,为广大用户带来了一个功能强大、方便实用的设计平台。板上还有千

2019-11-14 17:01

在FPGA系统设计中,要达到性能最大化需要平衡具有混合性能效率的元器件,包括逻辑构造(fabric)、片上存储器、DSP 和I/O带宽。在本文中,我将向你解释怎样能在追求更高系统级性能的过程中受益于Xilinx® 的Virtex™-5

2018-07-22 09:30

Virtex-6支持多种高速串行接口,其中高速串行模块GTX收发器可以实现150Mbit/s~6.5Gbit/s的线速率。GTX收发器是芯片与芯片之间、板与板之间进行串行通信的首选解决方案。

2017-02-11 09:26

部分可重构技术是Xilinx FPGA的一项重要开发流程。本文结合Virtex5 FPGA,详细讲解在ISE + Planahead上完成部分可重构功能的流程和技术要点。

2018-07-04 02:17

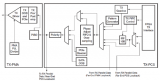

GTx接收和发送方向均由PCS和PMA两部分组成,PCS提供丰富的物理编码层特性,如8b/10b编码等;PMA部分为模拟电路,提供高性能的串行接口特性,如预加重与均衡。

2018-06-29 08:47

随着FPGA器件尺寸的增大及其内部设计密度的提高,时序收敛面临着前所未有的挑战。由于各种实现工具都竞相满足这种更高复杂性需求,把不同的实现转入量产时间越来越长。为了加快速度,有些设计人员希望能通过云计算来比较分析使用不同实现选项和用户约束决策的效果。

2017-11-18 12:02

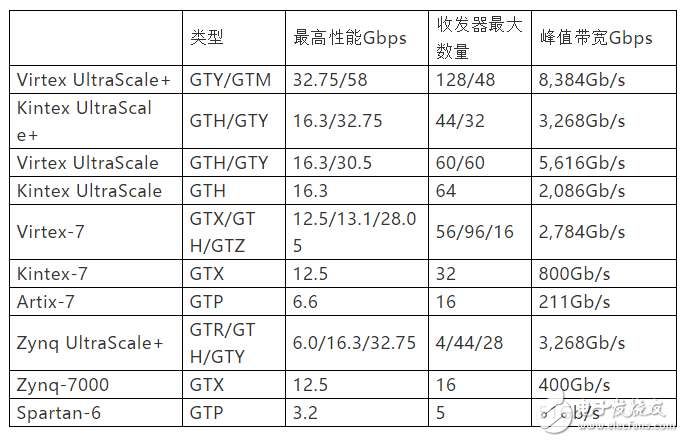

赛灵思Virtex® UltraScale ™ All Programmable FPGA 是高端FPGA 系列的扩展,可支持1Tbps 系统的实现。Virtex Ul

2017-11-18 04:15

为了能够灵活地验证和实现自主设计的基于NoC的多核处理器,缩短NoC多核处理器的设计周期,提出了设计集成4片Virtex-6—550T FPGA的NoC多核处理器原型芯片设计/验证平台。分析和评估了

2017-11-22 09:15