集赛灵思多年投资和35年架构之大成,基于7nm工艺,多核异构且能灵活改变,面向所有开发者和各种应用的Versal 宣布发货了!

2019-07-31 17:06

接着上一篇“AMD Versal系列CIPS IP核介绍”文章来进一步讲解如何来建立CIPS IP核示例工程。

2023-12-05 13:34

AMD 自适应计算文档按一组标准设计进程进行组织,以便帮助您查找当前开发任务相关的内容。您可以在设计中心页面上访问 AMD Versal 自适应 SoC 设计进程。您还可以使用设计流程助手来更深入了解设计流程,并找到特定于预期设计需求的内容。本文档涵盖了以下设计进程:

2025-06-03 14:25

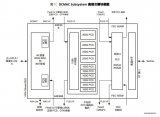

AMD自适应计算加速平台(ACAP)是一个完全软件可编程资源集合,这些资源结合在一起构成片上系统 (SoC),包括以下主要的资源块

2023-11-27 14:12

Versal HBM 栈可通过内部 HSM0 参考时钟来进行时钟设置,此参考时钟是由 CIPS 或外部时钟源生成的。

2023-06-05 09:41

Versal 系列的 DMA axi bridge 模式可以在 PL 的 QDMA IP 或者在 CPM(The integrated block for PCIe Rev. 4.0

2023-05-10 09:47

提出一种可进化IP核的设计和实现方法。这种IP核采用进化硬件的设计思想,将遗传算法运用于硬件电路的设计中,使电路能根据当

2021-06-22 14:37

为了应对无线波束形成、大规模计算和机器学习推断等新一代应用需求的非线性增长,AMD 开发了一项全新的创新处理技术 AI 引擎,片内集成该AI Engine的FPGA系列是Versal™ 自适应计算加速平台 (ACAP) 。

2024-04-09 15:14

Versal的DDR4是通过NoC访问,因此需要添加NoC IP进行配置。

2024-03-22 17:18

本次接着看下《UltraFast 嵌入式设计方法指南》中关于硬件设计方面的内容,主要分3部分:硬件设计需要考虑的事项、设计流程及个人总结。

2018-06-28 09:24