熟练了一点、但是整体编写下来比较零碎不成体系,所以在这里简要记录一下一般情况下、针对小型的verilog模块进行测试时所需要使用到的testbench文件的编写要点。

2023-08-01 12:44

在编写完HDL代码后,往往需要通过仿真软件Modelsim或者Vivadao自带的仿真功能对HDL代码功能进行验证,此时我们需要

2024-04-29 10:43

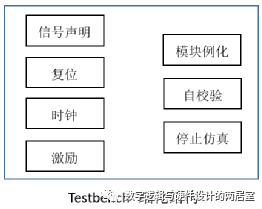

TestBench来进行仿真是一个很不错的选择。VHDL与Verilog语言的语法规则不同,它们的TestBench的具体写法也不同,但是应包含的基本结构大体相似,在V

2023-09-09 10:16

本讲使用matlab产生待滤波信号,并编写testbench进行仿真分析,在Vivado中调用FIR滤波器的IP核进行滤波测试,下一讲使用两个DDS产生待滤波的信号,第五讲或第六讲开始

2021-04-27 18:18

TestBench来进行仿真是一个很不错的选择。 VHDL与Verilog语言的语法规则不同,它们的TestBench的具体写法也不同,但是应包含的基本结构大体相似,在

2021-08-04 14:16

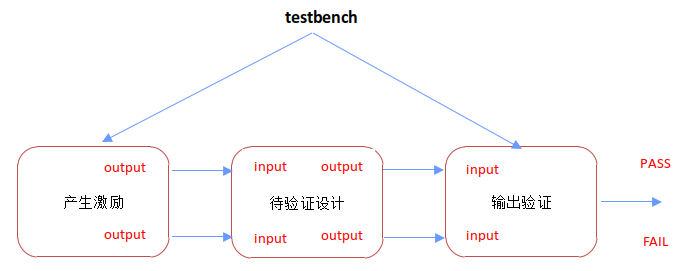

Testbench是验证HDL设计的主要手段,本文提供了布局和构建高效Testbench的指南以及示例。另外,本文还提供了一种示例,可以为任何设计开发自检Testbench

2024-10-29 16:14

在开始设计前,根据设计划分好各功能模块(为了叙述方便,这里以对“FPGA数字信号处理(十三)锁相环位同步技术的实现”中设计的系统仿真为例)。编写好第一个子模块(本例中为双相时钟生成模块),在Vivado中添加仿真si

2020-11-20 11:29

Verilog 代码设计完成后,还需要进行重要的步骤,即逻辑功能仿真。仿真激励文件称之为 testbench,放在各设计模块的顶层,以便对模块进行系统性的例化调用进行

2023-06-02 11:35

自动化验证testbench结果可以减少人工检查的时间和可能犯的失误,尤其对于比较大的设计。

2023-09-04 09:15

废话不多说直接上干货,testbench就是对写的FPGA文件进行测试的文件,可以是verilog也可以是VHDL。

2023-06-28 16:44