本文对如何在一个工程里例化和使用多个BSCANE2模块做一个简单说明。

2022-11-30 10:30

Verilog-2005中有3个generate 语句可以用来很方便地实现重复赋值和例化(generate for)或根据条件选择性地进行编译(generate if和generate case)等功能。接下来就一起

2022-12-28 15:21

无论是VHDL还是Verilog,建议初学者先掌握其中一门。

2017-12-19 13:09

Verilog和VHDL之间的区别将在本文中通过示例进行详细说明。对优点和缺点的Verilog和VHDL进行了讨论。

2023-12-20 09:03

Verilog规范对于一个好的IC设计至关重要。

2023-08-17 10:14

Verilog模块之间的连接是通过模块端口进行的。 为了给组成设计的各个模块定义端口,我们必须对期望的硬件设计有一个详细的认识。 不幸的是,在设计的早期,我们很难把握设

2023-06-12 10:05

本文首先介绍了verilog的概念和发展历史,其次介绍了verilog的特征与Verilog的逻辑门级描述,最后介绍了Verilog晶体管级描述与

2018-05-14 14:22

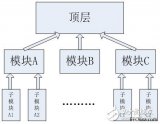

模块化设计是FPGA设计中一个很重要的技巧,它能够使一个大型设计的分工协作、仿真测试更加容易,代码维护或升级更加便利。

2018-05-02 14:49

Verilog 与 VHDL 比较 1. 语法和风格 Verilog :Verilog 的语法更接近于 C 语言,对于有 C 语言背景的工程师来说,学习曲线较平缓。它支持结构化

2024-12-17 09:44

Verilog设计的仿真需求。 编写测试文件 : 编写Verilog测试文件,对设计的各个模块进行测试。测试文件应覆盖各种情况,包括正

2024-12-17 09:50