使用Verilog进行数字电路设计是一个复杂但有序的过程,它涉及从概念设计到实现、验证和优化的多个阶段。以下是一个基本的步骤指南,帮助你理解如何使用Verilog来设计数字电路

2024-12-17 09:47

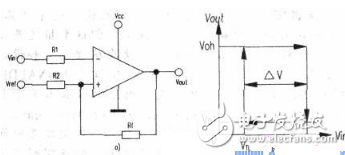

本文主要介绍了典型迟滞比较器电路图大全(四款典型迟滞比较器电路设计原理图详解)。迟滞比较器是一个具有迟滞回环传输特性的比较器。在反相输入单门限电压比较器的基础上引入正反

2018-03-26 16:51

在现代电子设计自动化(EDA)领域,Verilog作为一种硬件描述语言,已经成为数字电路设计和验证的标准工具。它允许设计师以高级抽象的方式定义电路的行为和结构,从而简化了从概念到硅片的整个设计流程

2024-12-17 09:53

关于Verilog语言的官方标准全称是《IEEE Std 1364-2001:IEEE Standard Verilog® Hardware Description Language》。其中包括27章以及8个附录,真正对于电

2018-07-06 09:59

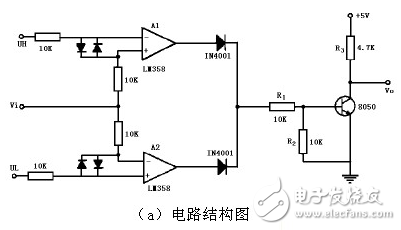

本文主要介绍了典型窗口比较器电路图大全(六款典型窗口比较器电路设计原理图详解)。窗口比较器,又称为双限比较器,具有两个门限电平,可以检测输入模拟信号的电平是否处在给定的

2018-02-27 08:42

本文主要介绍了典型光敏二极管电路图大全(八款典型光敏二极管电路设计原理图详解)。光敏二极管也叫做光电二极管,当受到光照的时候,里面的饱和反向漏增大,形成光电流,电流的强

2018-03-01 13:53

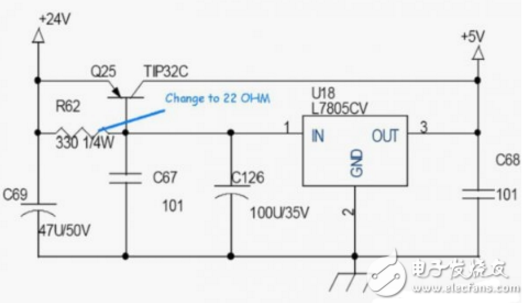

本文主要介绍了常见开关电源电路设计汇总(几款模拟电路设计原理图)。重点分析了几款开关电源的典型电路。开关电源的主要电路是

2018-01-24 17:10

HDLBits 是一组小型电路设计习题集,使用 Verilog/SystemVerilog 硬件描述语言 (HDL) 练习数字硬件设计~

2022-08-31 09:06

本文首先介绍了verilog的概念和发展历史,其次介绍了verilog的特征与Verilog的逻辑门级描述,最后介绍了Verilog晶体管级描述与

2018-05-14 14:22

Circuit,专用集成电路)设计是一个复杂的过程,涉及到逻辑设计、综合、布局布线、物理验证等多个环节。在这个过程中,Verilog被用来描述数字电路的行为和结构,进而实现ASIC的设计。 具体来说

2024-12-17 09:52