VCS是编译型verilog仿真器,VCS先将verilog/systemverilog文件转化为C文件,在linux下编译生成的可执行文./simv即可得到仿真结果。

2022-05-23 16:04

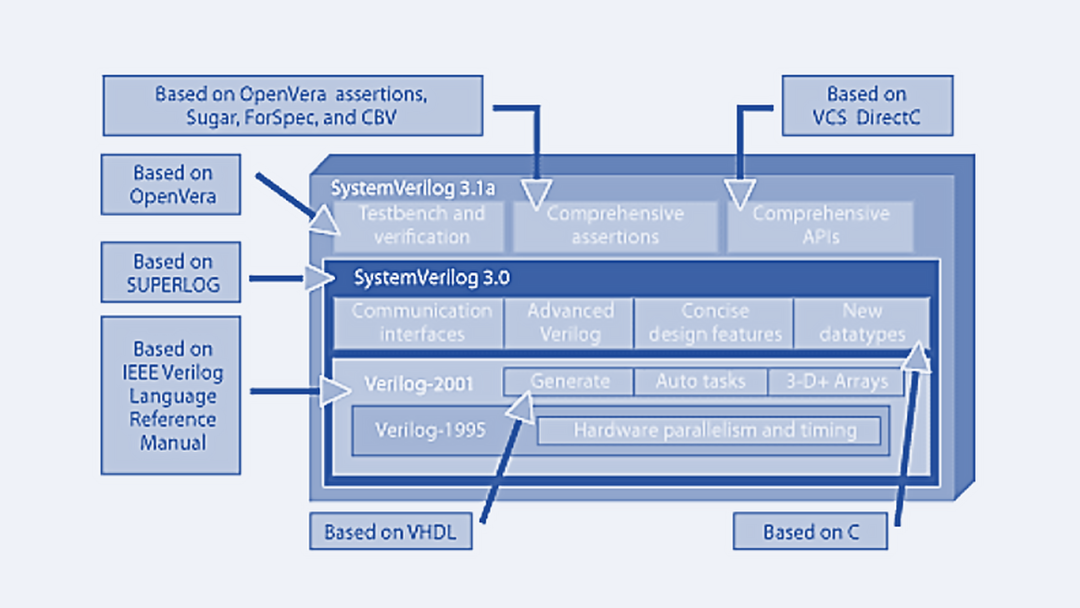

SystemVeirlog的全面支持是开发商用仿真器的第一道门槛。市面上可以找到不少基于纯Verilog的仿真器,但是真正能完整支持SystemVerilog 的仍然屈指可数。如何全面地支

2023-04-07 14:40

VCS是编译型verilog仿真器,VCS先将verilog/systemverilog文件转化为C文件,在linux下编译生成的可执行文./simv即可得到仿真结果。

2023-05-30 09:26

VCS是编译型verilog仿真器,VCS先将verilog/systemverilog文件转化为C文件,在linux下编译生成的可执行文./simv即可得到仿真结果。

2023-10-25 17:22

Verilog HDL语言不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。因此,用这种语言编写的模型能够使用Verilog仿真器进行验证。语言从C编程语

2019-09-27 07:09

SystemVeirlog的全面支持是开发商用仿真器的第一道门槛。市面上可以找到不少基于纯Verilog的仿真器,但是真正能完整支持SystemVerilog 的仍然屈指可数。如何全面地支持SystemVerilog

2023-07-14 15:15

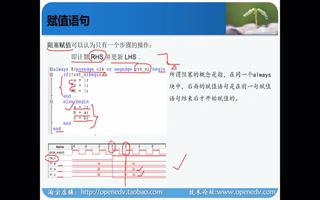

赋值何时使用阻塞赋值才能设计出符合要求的电路。 他们也不完全明白在电路结构的设计中,即可综合风格的Verilog模块的设计中,究竟为什么还要用非阻塞赋值,以及符合IEEE 标准的Verilog 仿真器究竟如何来处理非

2021-08-17 16:18

Verilog HDL语言不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。因此,用这种语言编写的模型能够使用Verilog仿真器进行验证。语言从C编程语

2019-09-19 07:06

只作为语法设定来介绍,忽略了Verilog语言的软件特性和仿真特性。使得初学者无法理解Verilog语言在行为级语法(过程块、赋值和延迟)背后隐藏的设计思想。本文尝试从仿真器

2023-05-25 15:10

只作为语法设定来介绍,忽略了Verilog语言的软件特性和仿真特性。使得初学者无法理解Verilog语言在行为级语法(过程块、赋值和延迟)背后隐藏的设计思想。本文尝试从仿真器

2023-05-25 15:10