内置自测(BIST),曾经保留用于复杂的数字芯片,现在可以在许多具有相对少量数字内容的设备中找到。

2019-04-12 14:14

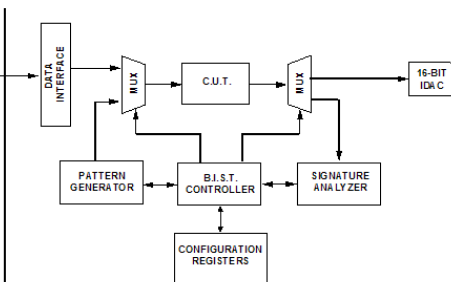

在系统层面,BIST功能可用于设计阶段,以表征数字处理器和数据转换器之间的数字接口时序。如果没有BIST,数字接口中的位错误必须通过转换器本底噪声的变化来检测。这种类型的错误检测远不如基于数字

2023-02-01 15:36

利用FPGA可重复编程的特性,通过脱机配置,建立BIST逻辑,即使由于线路被操作系统的重新配置而令BIST结构消失,可测性也可实现。本文给出一种基于BIST利用ORCA(Optimized

2018-11-28 09:02

基于BIST的编译码器IP核测 随着半导体工艺的发展,片上系统SOC已成为当今一种主流技术。基于IP复用的SOC设计是通过用户自定义逻辑(UDL)和连线将IP核整合

2008-12-27 09:25

数字BIST的工作原理:用一个LFSR(线性反馈移位寄存器)生成伪随机的位模式,并通过临时配置成串行移位寄存器的触发器,将这个位模式加到待测电路上。

2011-11-23 15:24

BIST在SoC片上嵌入式微处理器核上的应用 引 言 随着科技的不断发展,集成电路的制造工艺和设计水平得到了飞速提高,设计者能够将非常复杂的功能集成到

2009-11-07 11:18

随着当今汽车中芯片数量的快速增长,IC设计人员需要改进流程以满足ISO 26262标准定义的功能安全(FuSa: Function Safety)要求。

2024-01-25 12:38

就是SRAM MBIST_CLK延时下来刚好和SRAM测试地址TADDR的跳变完全对齐了,造成了SRAM的memory model的建立/保持时间违例,SRAM model在timing违例情况下Q端输出为X态。下文具体内容请移步知识星球查看。

2023-02-08 16:09