随着半导体技术的快速发展,集成电路芯片的复杂度日益增加,芯片设计中的验证工作变得越来越重要。验证的目的是确保芯片在各种工况下的功能正确性和性能稳定性。在这个过程中,testcase(测试用例)扮演着关键角色。本文将简要介绍 testcase 的基本概念、设计方法和

2023-09-09 09:32

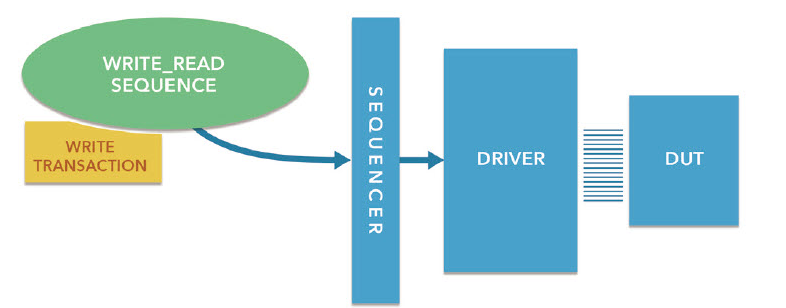

SystemVerilog通用验证方法(UVM)是一种生成测试和检查结果以进行功能验证的有效方法,最适合用于块级IC或FPGA或其他“小型”系统。在UVM测试台中,大多数活动是通过编写序列来生

2021-04-09 16:09

nohup命令用于运行程序或者命令,并忽略所有中断信号SIGHUP。SIGHUP是当前控制终端关闭时发送到进程的信号。

2022-12-05 16:25

本篇是对UVM设计模式 ( 二 ) 参数化类、静态变量/方法/类、单例模式、UVM_ROOT、工厂模式、UVM_FACTORY[1]中单例模式的补充,分析静态类的使用,UVM

2023-08-06 10:38

当我们在创建动态仿真case时,使用命令行参数可以非常方便地控制DUT和TB的行为,比如配置寄存器、控制激励的发送数量、打开或关闭某些scoreboard等。

2022-08-19 11:53

在上篇 LTspice 系列文章中,我们分享了如何利用ISO模型进行电源线瞬态电传导干扰测试,本文将介绍使用 .func 命令中的指定常数以有效运行仿真并进行参数分析的方法。更多参数分析的内容,可查阅《活学活用LTspice进行电路设计 — 用 .step

2025-01-14 16:48

ISP算法仿真中,小编会用reference model调用DPI接口用C++ 算法实现pixel算法处理,然后和DUT算法处理输出的pixel值进行比较,比较时候发现报错,报错代码如下,原因是小编把uvm1.1升级为uvm1.2了。

2024-03-04 14:18

我们在项目中有时候需要使用不同的UVM版本库进行仿真,有时候还会在不同的仿真器之间进行切换,本文简单总结了一下vcs和xrun搭配uvm1.1/uvm1.2版本库的使用情况,希望能帮助到一些朋友。

2023-10-27 09:41

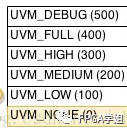

UVM预先定义了六个详细程度; UVM_NONE到UVM_DEBUG。这些级别只不过是整数枚举值

2023-06-06 12:33

我们常用的debug UVM的方法是通过打印log实现。有没有办法像 debug RTL代码一样将 UVM 中变量拉到波形上看呢?答案是有的,下面让我们看看是怎么做到的。

2023-06-25 16:01