电路设计充满挑战,即便是最富经验的工程师也难免遭遇困惑与阻碍。《电路设计常见问题解答》是ADI精心筹备的一份实用指南,力求为您铺设一条清晰的学习与实践之路。

2024-11-05 17:02

Xilinx采用首个ASIC级UltraScale可编程架构之首款20nm All Programmable器件开始投片常见问题解答:什么是UltraScale 架构?ASIC 级 UltraScale 架构能为赛灵思 FPGA、3D IC 和 SoC 带来哪些优势?

2013-07-09 20:28

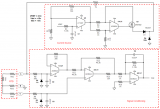

在Basic元件组中有一个便于使用的元件——跳线, 如图4所示。它看上去像一个倒下的字母T。跳线可以用来连接相似的、 相关的电路功能, 如V+、 V–或任何其它具有多连接的电路点。使用跳线能减少布线带来的杂乱。值得注意的是,共用的跳线必须被标记为相同的TINA-TI标签名称, 才表示它们连在一起。

2022-10-17 11:09

您是否希望学习 RS-485 收发器的设计教程?本文基于 TI E2E 社区中的常见问题提供了一些解答,如果您希望详细了解此通信标准,这将是非常有用的资源。

2023-03-07 17:55

随着接入网络的终端越来越多,网络规模越来越大,但是二层交换机的容量和性能有限,无法接入日益增多的终端。于是就有了三层网络设备路由器,连接不同网段的二层交换机,进而把全世界的网络都连接起来。接下来我们看看关于路由器的常见问题。

2023-08-28 16:12

防水试验机是保证产品防水性能的重要工具。但是,在使用过程中,我们可能会遇到一些常见的问题和故障。本文将为您介绍防水试验机常见问题的答案和故障排除方法,帮助您更好地使用该设备。一、解答

2025-01-06 14:16 岳信仪器气密性检测仪 企业号

Revit 版 Twinmotion 和面向 Revit 的 Datasmith 导出器插件安装完毕后,视图选项卡会显示新的 Twinmotion 功能区按钮,其中包含新的在 Twinmotion 中打开命令以及面向 Revit 的 Datasmith 导出器命令。

2023-02-23 09:24

为何现在串口速率比并口速率要快? 并行通信的瓶颈:并行数据传输技术向来是提高数据传输率的重要手段,但是,进一步发展却遇到了障碍。首先,由于并行传送方式的前提是用同一时序传播信号,用同一时序接收信号,而过分提升时钟频率将难以让数据传送的时序与时钟合拍,布线长度稍有差异,数据就会以与时钟不同的时序送达,另外,提升时钟频率还容易引起信号线间的相互干扰,导致传输错误。

2018-05-22 05:47

随着信号的速率越来越高,调制格式越来越复杂,对测试仪器的性能要求也越来越高。是德科技也一直在推出业界领先的高带宽、高采样率的AWG和高性能的BERT。

2024-08-06 17:27