以Altera公司的FPGA EP2S60为例,探讨了SOPC系统设计的综合优化方法。

2012-03-12 11:49

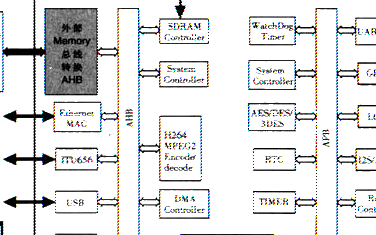

随着硅片集成技术的高速发展,片上系统SoC(system-on-a-Chip)已经成为现代数字系统设计的必然趋势。SoC和一般数字系统最主要的区别是前者在单一硅片内集成了独立的嵌入式CPU,必要的存储器控制器也要求集成到SoC芯片内,所以对SoC系统的软硬件协同实时验证便成为SoC设计的难点。

2021-03-17 17:04

观看这一视频演示,了解Stratix® II GX FPGA是怎样帮助您任意改变背板卡的位置,同时全面保持信号完整性不变的。利用Stratix II GX FPGA的即

2018-06-22 03:56

Altera推出业界密度最大的Stratix IV EP4SE820 FPGA Altera宣布,40-nm Stratix IV E FPGA高端密度范围增大到业界领先的820K逻辑单元(LE)。

2009-11-11 16:50

μC/OS-II在EP7312上的移植首先介绍μC/OS-II操作系统的特点,重点分析μC/OS-II在EP7312上的

2009-06-16 11:24

)。Stratix IV EP4SE820 FPGA是业界同类产品中密度最大、性能最好、功耗最低的FPGA。EP4SE820 FPGA非常适合各种需要大容量FPGA的高端数字应用,包括ASIC原型开发和仿真

2018-10-24 20:40

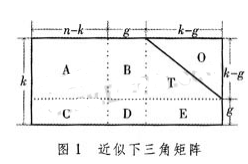

低密度奇偶校验(Low Densitv Paritv Check,LDPC)码已成为当今信道编码领域的研究热点之一。LDPC码属于线性分组码,根据其构造方法和相应的编码算法,主要分为两类:一类是随机构造的LDPC码,该类码在长码时具有很好的纠错能力,然而由于码组过长,以及生成矩阵与校验矩阵的不规则性,使编码过于复杂而难以用硬件实现,编码时间过长也不利于硬件的实时应用;另一类是结构码,它由几何、代数和组合设计等方法构造。大多数LDPC结构码是循环或准循环结构,准循环码在中短码时具有相当强的纠错能力,性能接近随机构造的最优LDPC码,又因其硬件实现极其简单,只需用反馈移位寄存器连接就可实现,因此具有很好的应用前景。

2020-09-21 17:23

极高的性能和密度,而且还针对器件总功率进行了优化,同时可以支持高达1 Gbps的高速差分I/O信号,因而是一款超快的FPGA。该芯片中所含的高性能嵌入式DSP块的运行频率高达370 MHz。另外Stratix II还

2020-12-10 11:42

Tensilica推出HiFi EP音频DSP Tensilica宣布即将推出基于HiFi 架构的新一代产品HiFi EP音频DSP,可同时支持家庭娱乐产品中的多声

2010-02-09 10:48

S2C Inc.宣布在Altera公司的40-nm StraTIx IV现场可编程逻辑闸阵列(FPGA)基础上发布其第四代快速SoC原型工具,即S4 TAI Logic Module。 Dual

2010-07-01 08:50