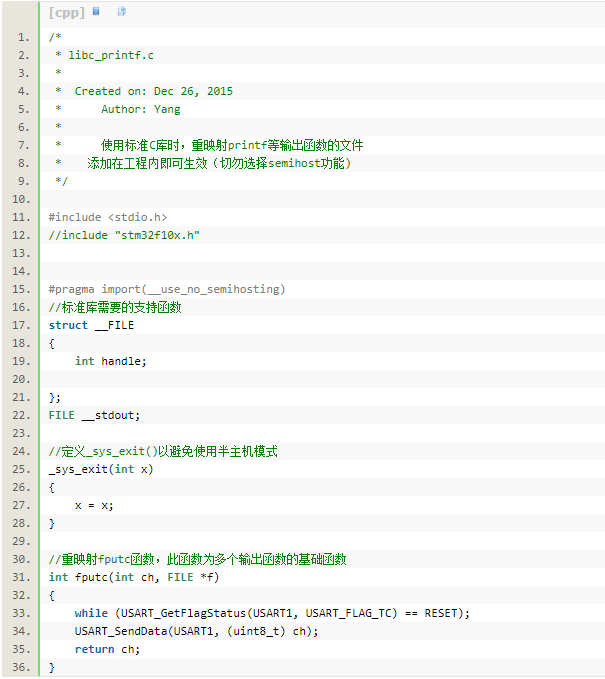

该方法适用于 STM32 ,实现了使用printf等标准C流函数输出数据的办法,极大的减少了输出 串口数据 时所需要做的数据处理。 实现原理 在C库中,printf()等输出

2018-06-21 07:51

先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输出

2020-03-29 17:19

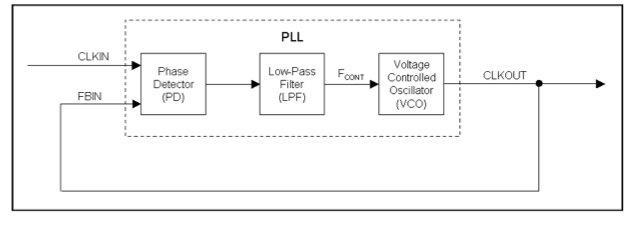

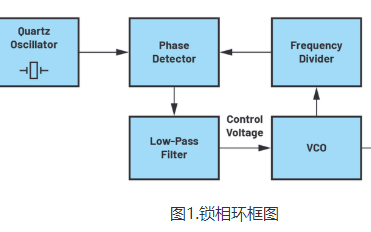

本应用报告介绍了实现 IDT 基于 PLL 的零延迟缓冲器的输入参考时钟和输出时钟之间定义的相位关系的不同方法。该报告重点介绍了 PLL 反馈环路中不同走线长度和反馈时钟输入端的电容负载对生成早期

2021-06-15 10:48

当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的时间称为锁定时间,这是PLL设计最关键的参数之一。

2018-03-14 15:17

锁相环(PLL)电路是由压控振荡器(VCO)和鉴相器组成的反馈系统,振荡器信号跟踪施加的频率或相位调制信号是否具有正确的频率和相位。需要从固定低频率信号生成稳定的高输出频率时,或者需要频率快速变化时,都可以使用PLL

2020-10-06 14:43

STM32中有一个全速功能的USB模块,其串行接口引擎需要一个频率为48MHz的时钟源。该时钟源只能从PLL输出端获取,可以选择为1.5分频或者1分频,也就是,当需要使用USB模块时,

2017-11-30 09:14

本实验活动介绍锁相环(PLL)。PLL电路有一些重要的应用,例如信号调制/解调(主要是频率和相位调制)、同步、时钟和数据恢复,以及倍频和频率合成。在这项实验中,您将建立一个简单的PLL电路,让您对

2023-07-10 10:22

获得高频输出的方法(第一部:锁相环电路)锁相环电路概略与爱普生产品阵容【序文】近年,伴随影像传输等普及,骨干网中流过的通信量有增无减,通信的高速、大容量化进展迅速。在这种情况下,高速化通信基础设施

2024-08-15 14:10 Piezoman压电侠 企业号

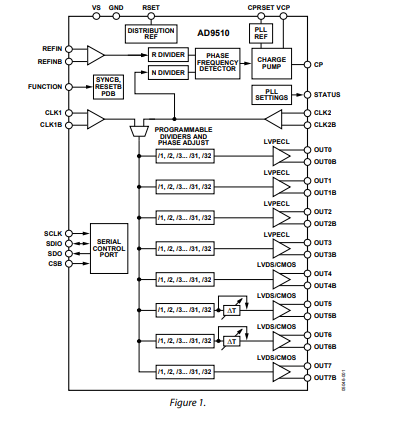

AD9510提供多路输出时钟分配功能,并集成一个片内锁相环(PLL)内核。它具有低抖动和低相位噪声特性,能够极大地提升数据转换器的时钟性能。4路独立的LVPECL时钟输出和4路LVDS时钟

2025-04-15 11:41

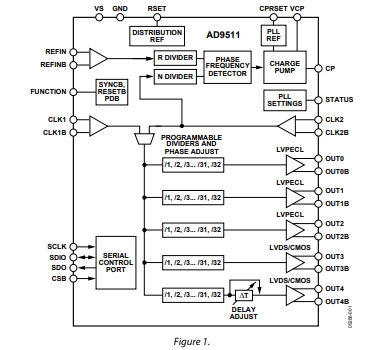

AD9511提供多路输出时钟分配功能,并集成一个片内锁相环(PLL)内核。它具有低抖动和低相位噪声特性,能够极大地提升数据转换器的时钟性能。3路独立的LVPECL时钟输出和2路LVDS时钟

2025-04-15 13:48