晶振是电子设备中用于产生稳定时钟信号的关键元件,其短期稳定度直接影响设备的精度和可靠性。短期稳定度是指晶振在短时间内(通

2024-12-30 15:08

环路稳定度是控制系统、电源设计等领域中一个重要的概念,用于衡量一个闭环系统在受到干扰或参数变化时保持稳定的能力。

2025-03-05 18:08

振荡电路需要满足频率稳定度,温度特性,电源电压特性等条件。为设计性能均衡的振荡电路,我们需要权衡不同的电气参数。

2023-05-05 15:06

在选购或者使用晶振时,我们经常会听到频率准确度和频率稳定度这两个概念。虽然两者都与晶振的频率变化相关,但它们的关注重点不同。

2025-02-25 18:07

在FPGA设计中,PLL(锁相环)模块作为核心时钟管理单元,通过灵活的倍频、分频和相位调整功能,为系统提供多路高精度时钟信号。它不仅解决了时序同步问题,还能有效消除时钟偏移,提升系统稳定性。本文将深入探讨智多晶PLL

2025-06-13 16:37

相位裕度与增益裕度都是用于评估放大器的稳定性的参数。其中,相位裕度使用更为普遍。本篇将介绍使用相位裕度分析放大器

2023-02-22 13:59

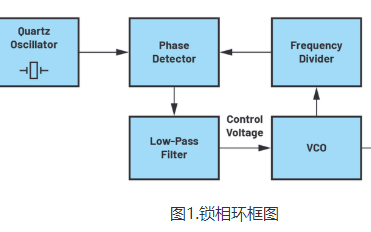

锁相环(PLL)电路是由压控振荡器(VCO)和鉴相器组成的反馈系统,振荡器信号跟踪施加的频率或相位调制信号是否具有正确的频率和相位。需要从固定低频率信号生成稳定的高输出频率时,或者需要频率快速变化时,都可以使用PLL

2020-10-06 14:43

当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的时间称为锁定时间,这是PLL设计最关键的参数之一。

2018-03-14 15:17

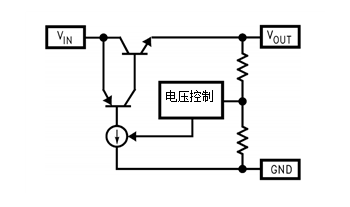

输出稳定度对于任何电源设计而言都是一项关键问题。由于线性稳压器简单易用(多数线性稳压器只有三个插脚),所以很容易忘记这一点的重要性。虽然目前具有许多能够确保输出稳定的技术,但最简单且最经济有效的方案是添加或使用输出电

2022-02-06 09:43

输出稳定度对于任何电源设计而言都是一项关键问题。由于线性稳压器简单易用(多数线性稳压器只有三个插脚),所以很容易忘记这一点的重要性。虽然目前具有许多能够确保输出稳定的技术,但最简单且最经济有效的方案是添加或使用输出电

2016-04-30 06:31