STM32中有一个全速功能的USB模块,其串行接口引擎需要一个频率为48MHz的时钟源。该时钟源只能从PLL输出端获取,可以选择为1.5分频或者1分频,也就是,当需要使用USB模块时,PLL必须使能,并且时钟频率配置

2017-11-30 09:14

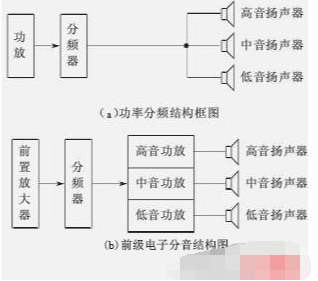

从分频方式看可以分为两种,一种是主动分频(PassiveCrossover),或者叫电子分频,也可以叫外置分频、有源分频

2019-10-08 10:37

在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,下面就介绍一下在vivado2017.3中进行PL开发时调用IP的方法。

2018-12-22 14:26

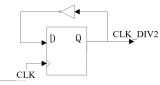

初学 Verilog 时许多模块都是通过计数与分频完成设计,例如 PWM 脉宽调制、频率计等。而分频逻辑往往通过计数逻辑完成。本节主要对偶数分频、奇数分频、半整数

2023-03-29 11:38

在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,这是同步时序电路的关键,这时就需要使用到时钟向导IP,下面就介绍一下在vivado中进行PL开发时调用IP的方法。

2018-12-22 15:14

缺点:当分频倍数很大时,需要的寄存器也是倍增。当然你也可以采用复用的方式去减少所需寄存器数目,例如,36分频,可以做两个6分频器相连,则所需寄存器为6个,需要的寄存器数大大减少。

2018-12-08 10:40

两路两分频系统的中低音/高音的分频点的选择,除了要遵循关于中低音,高音的特性选择外,一般地,在汽车音响中由于两分频系统的单元距离较远,分频点宜低不宜高,这可以尽量避免中

2019-10-09 09:29

STM32—数组作为被调用函数的入口参数时,要两个条件, 1:数组首地址 2:数组长度 在被调用函数中,比如把数据保存到数组pbuffer[ ]中,那么在入口参数定义时要定义成指针u8 *pbuff

2018-12-18 15:05

分频点是分频器分配给每个扬声器单元所承担的频响范围的标记,是根据扬声器单元的音频表现能力(单元振膜有效直径决定的边界频率)而定的;那么,三分频最佳分频点是多少?

2019-10-09 09:56

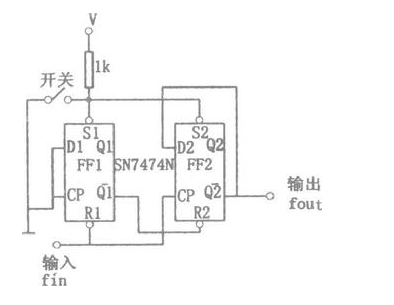

所谓“分频”,就是把输入信号的频率变成成倍数地低于输入频率的输出信号。数字电路中的分频器主要是分为两种:整数分频和小数分频。其中整数

2023-03-23 15:06