signed 关键字定义输入端口的数据类型为有符号数 input signed [7:0] a; input signed [7:0] b; //通过 signed 关键字定义寄存器的

2018-10-09 15:22

为了省流,还是先甩结论。有符号数和无符号数的最本质区别就是:符号位的识别和高位拓展。除此之外,另一个区别就是从人的角度如何如何读这个数,或者说$display(%d)打

2023-12-10 10:50

我们学习一下Systemverilog中的有符号数据类型的赋值。

2022-10-17 14:40

在数字电路中,出于应用的需要,我们可以使用无符号数,即包括0及整数的集合;也可以使用有符号数,即包括0和正负数的集合。在更加复杂的系统中,也许这两种类型的数,我们都会用到。 有

2020-11-18 17:46

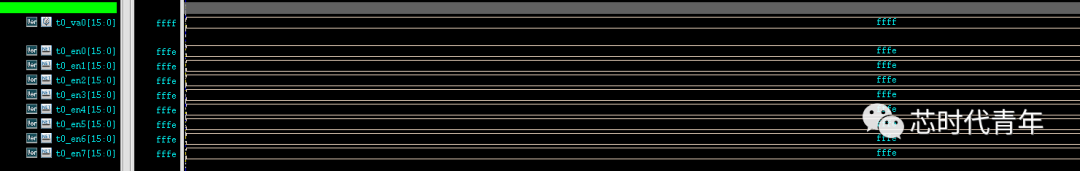

有符号数的计算在 Verilog 中是一个很重要的问题(也很容易会被忽视),在使用 Verilog 语言编写 FIR 滤波器时,需要涉及到有符号数的加法和乘法,在之前的

2021-05-02 10:48

不知道有没有人像我一样,长久以来将verilog中的有符号数视为不敢触碰的禁区。

2023-12-04 16:13

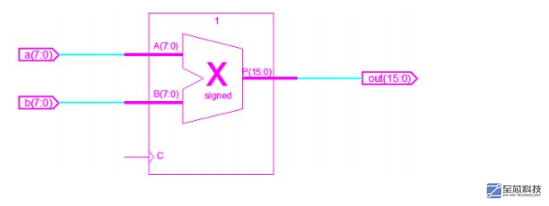

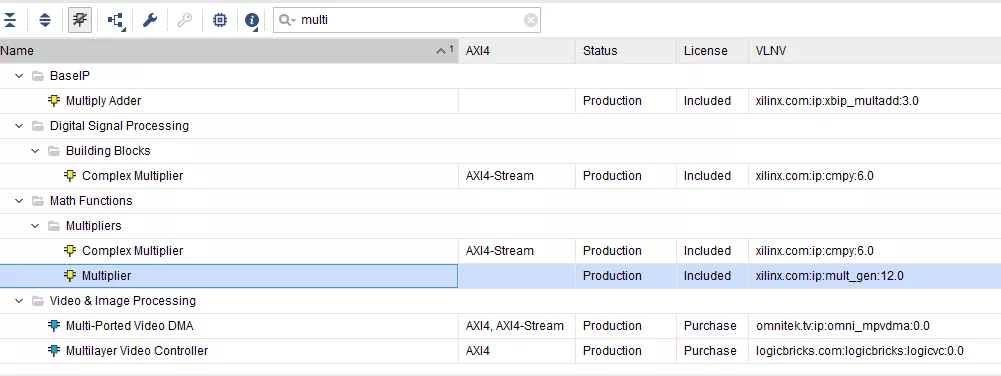

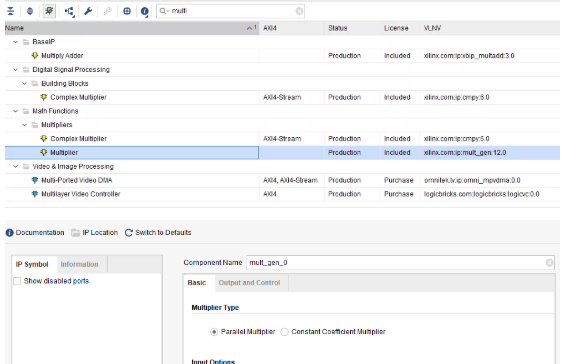

FPGA中乘法器是很稀缺的资源,但也是我们做算法必不可少的资源。7系列及之前的FPGA都是25x18的DSP,UltraScale中是27x18,我们可以通过调IP Core的方式或者原语的方式来进行乘法操作。在里面可以设置有符号还是无

2022-02-16 16:21

FPGA中乘法器是很稀缺的资源,但也是我们做算法必不可少的资源。7系列及之前的FPGA都是25x18的DSP,UltraScale中是27x18,我们可以通过调IP Core的方式或者原语的方式来进行乘法操作。在里面可以设置有符号还是无

2020-03-08 17:14

输入系统的有正有负的模拟信号在AD采样前,会加上了直流偏置变成全正信号才输入AD的,所以在AD采样后送给FPGA的信号是无符号数。

2019-08-11 11:43

单字节无符号数据块排序(增序) 入口条件:数据块的首址在R0中,字节数在R7中。出口信息:完成排序(增序)影响资源

2009-01-19 22:58