74LS74内含两个独立的D上升沿双d触发器,每个触发器有数据输入(D)、置位输入( )复位输入( )、时钟输入(CP)和数据输出(

2021-06-04 15:40

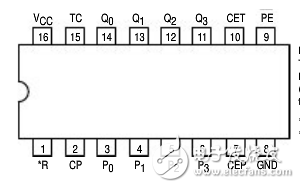

数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。而只有当CR=LD=EP=ET=“1”、CP脉冲上升沿作用后

2018-05-08 11:07

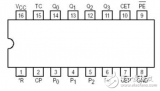

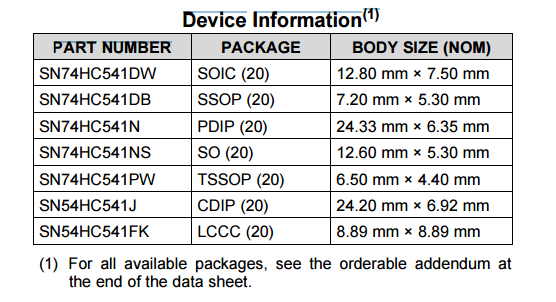

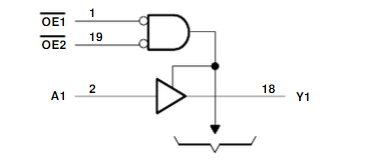

这些八口通道缓冲器和线路驱动器具有SN74HC541器件的性能以及封装两侧输入和输出的引脚排列。 这种布置极大地方便了印刷电路板布局。三态输出由双输入NOR门控制。 如果输出使能(OE1或OE2)输入为高电平,则所有八个输出都处于高阻态。

2018-10-24 15:04

。通过模拟测量组件与独立于主 CPU 工作的状态机处理接口相结合,本文以德州仪器 (TI) 的 MSP430FW42x 系列16位MCU为例,给出超低功耗运动检测系统解决方案的清晰说明。

2018-01-18 09:05

通,允许Q0~Q7输出,OE为高电平时,输出悬空。当74LS373用作地址锁存器时,应使OE为低电平,此时锁存使能端C为高电平时,输出Q0~

2017-12-05 09:28

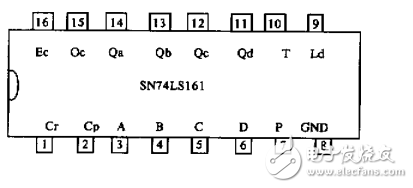

本文主要介绍了SN74LS161在数字电路中的抗干扰应用。SN74LS161是同步、可预置的4位二进制计数器。计数器除用于计数之外,通常还可以作为移存器、延时电路及各种脉冲波形产生器使用。实践证明利用计数器实现在数字电路中消除干扰,这是一种行之有效的方法。

2018-01-18 09:22

74hc164d 是高速硅门 CMOS 器件,与低功耗肖特基型 TTL (LSTTL) 器件的引脚兼容。74hc164d 是 8 位边沿触发式移位寄存器,串行输入数据,然后并行输出。数据通过两个输入

2017-10-22 10:10

”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端

2018-01-17 17:49

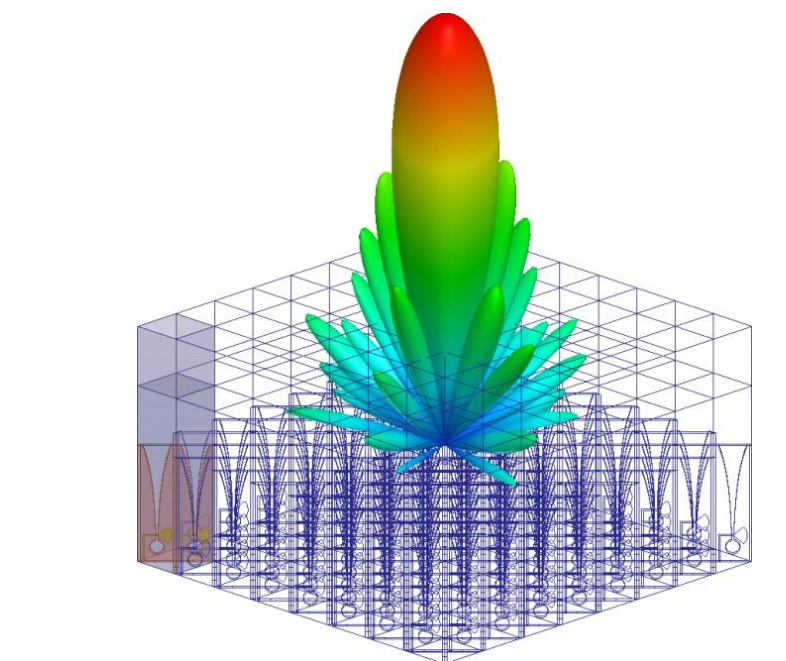

HFSS和Q3D的共同之处在于两者都支持对3D任何结构的建模和分析,最后都能得到该结构的等效模型。区别体现在如下几个方面。

2018-04-16 15:01

SN74HC541N集成块由八通道缓冲器和线路驱动器组成,这些八通道缓冲器和线路驱动器具有74HC240器件的性能以及封装两侧输入和输出的引脚排列。 这种布置极大地方便了印刷电路板布局。

2018-10-24 14:35