+3.3V;由于差分驱动与接收芯片的传输方向是单向的,而系统要求双向数据传输,对16位数据总线的高8位和低8

2021-03-19 11:35

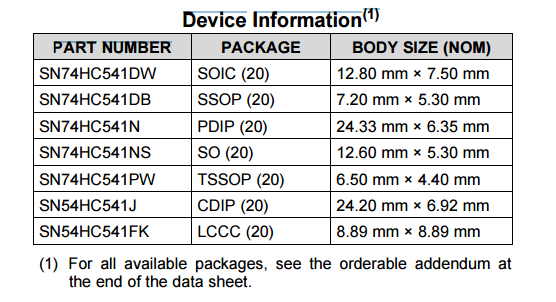

SN74HC541N集成块由八通道缓冲器和线路驱动器组成,这些八通道缓冲器和线路驱动器具有

2018-10-24 14:35

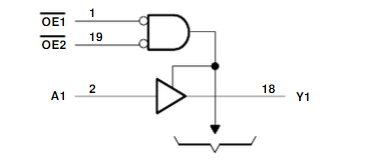

这些八口通道缓冲器和线路驱动器具有SN74HC541器件的性能以及封装两侧输入和输出的引脚排列。 这种布置极大地方便了印刷电路板布局。三态输出由双输入NOR门控制。 如果输出使能(OE1或OE2)输入为高电平,则所有

2018-10-24 15:04

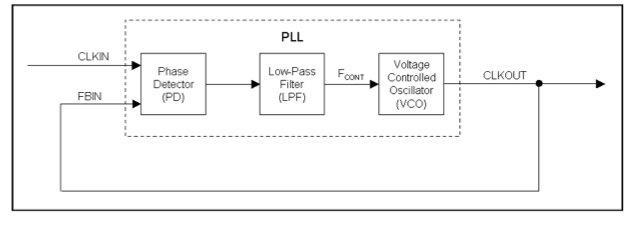

(或晚期)时钟的影响。早期时钟定义为输出时钟的相位相对于参考输入时钟提前的情况。 简介 时钟驱动器架构有两种主要类型:缓冲器型和带锁相环 (PLL) 的反馈型。在缓冲器型(非 PLL)时钟

2021-06-15 10:48

什么是时钟缓冲器(Buffer)?时钟缓冲器(Buffer)参数解析 什么是时钟缓冲器(Buffer)?我们先把这个概念搞清楚。 时钟缓冲器就是常说的Clock Buf

2022-10-18 18:36

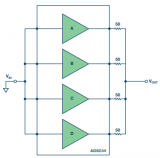

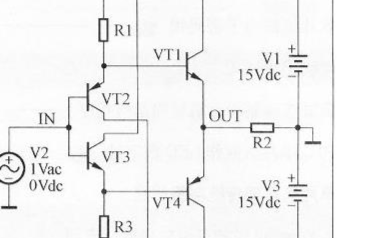

想要降低系统中增加的噪声,必须降低电压噪声。常用方法——并联放置多个缓冲器可降低电压噪声。但是,该方法会使偏置电流、电流噪声、输入电容,统统提高,这时,你需要一款4通道JFET缓冲放大器! 缓冲器是什么? 许多电子电

2018-05-27 05:13

三态数据缓冲器是数据输入/输出的通道,数据传输的方向取决于控制逻辑对三态门的控制。本文介绍三态缓冲器的逻辑符号。

2018-01-11 10:42

buffer缓冲器电路图与buffer电路示意图 buffer缓冲器的作用 buffer译名为: 缓冲,缓冲器,缓冲液;

2022-10-18 19:01

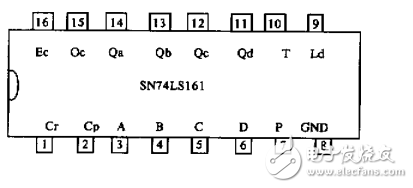

本文主要介绍了SN74LS161在数字电路中的抗干扰应用。SN74LS161是同步、可预置的4位二进制计数器。计数器除用

2018-01-18 09:22

MAX13256具有可调过流门限,用于短路保护。不幸的是,这个阈值使得使用标准方法为设备设计缓冲器变得困难。本应用笔记介绍了如何为MAX13256设计电压缓冲器,同时考虑限流特性。

2023-06-25 14:22