本方案是以CME最新的低功耗系列FPGA的HR03为平台,实现8/10b的SerDes接口,包括SERDES收发单元,通过完全数字化的方法实现SERDES的CDR(Cl

2019-05-24 15:33

随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立的ASSP 或ASIC 器件。在过去几年中已经看到有内置

2015-02-02 17:32

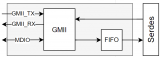

SGMII(Serial Gigabit Media Independent Interface) 通过将网络数据与控制接口进行转换,将复杂的GMII接口转换为一对serdes

2025-08-07 13:56

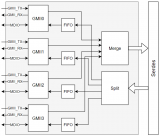

QSGMII(Quad Serial Gigabit Media Independent Interface) 旨在将4个GMII接口转换为一个统一的5Gb/s速率的SERDES接口,极大地减少了PHY与MAC间连接

2025-07-29 09:19

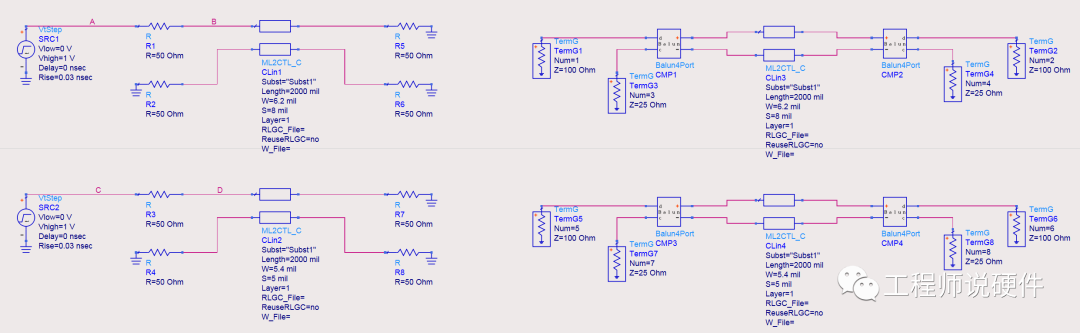

本章我们开始《信号完整性基础》 系列第五章节差分信号相关知识的讲解。随着信号速率的不断提高,传统并行接口的应用挑战越来越大,基于差分信号的Serdes接口越来越普及,差分信号在其中的重要性不言而喻。

2023-06-09 10:37

EXOSTIV Probe从各方面都优于传统调试方案,它支持Xilinx所有系列,采用高速SerDes接口实现数据采集和通信,EXOSTIV Probe能够采集多达32768个内部信号节点,此外EXOSTIV IP提供动态多路复用控制功能,能够动态采集更多的数据集

2018-06-28 15:56

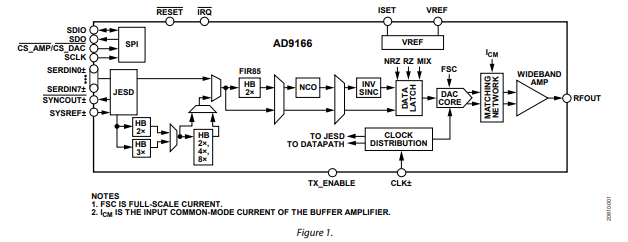

AD9166是高性能、宽带、片内矢量信号发生器,由高速 JESD204B 串行器/解串器(SERDES)接口、灵活的 16 位数字数据路径、正交 (IQ) 数模转换器 (DAC) 内核以及一个集成的差分至单端输出缓冲放大器组成 ,可匹配高达 10 GHz 的 50

2025-04-30 15:33

FPGA发展到今天,SerDes(Serializer-Deserializer)基本上是器件的标配了。从PCI发展到PCI-E,从ATA发展到SATA,从并行ADC接口到JESD204,从RIO到

2023-10-16 14:50

SerDes是一种功能块,用于对高速芯片间通信中使用的数字化数据进行序列化和反序列化。用于高性能计算(HPC)、人工智能(AI)、汽车、移动和物联网(IoT)应用的现代片上系统(SoC)都实现了

2025-03-27 16:18

SERDES是英文SERializer(串行器)/DESerializer(解串器)的简称。

2024-01-04 09:04