SystemVerilog引入了interface,这里我们从可综合的RTL代码的角度聊聊interface。

2023-10-12 09:06

在Vivado FlowNavigator中有一个Elaborated Design,如下图所示,属于RTL Analysis这一步对应的设计。可能很多工程师都没有使用到,而实际上对于代码优化,它是很有帮助的。

2020-10-21 10:56

引言 硬件描述语言(verilog,systemVerilog,VHDL等)不同于软件语言(C,C++等)的一点就是,代码对应于硬件实现,不同的代码风格影响硬件的实现效果。好的代码风格能让硬件跑得

2020-11-20 15:51

用软件从 C 转化来的 RTL 代码其实并不好理解。今天我们就来谈谈,如何在不改变 RTL 代码的情况下,提升设计性能。 本项目所需应用与工具:赛灵思HLS、Pluni

2020-12-20 11:46

当在SpinalHDL中调用别人的RTL代码时,需要采用BlackBox进行封装。对于大多数场景,想必小伙伴们都已轻车熟路。

2023-07-12 16:21

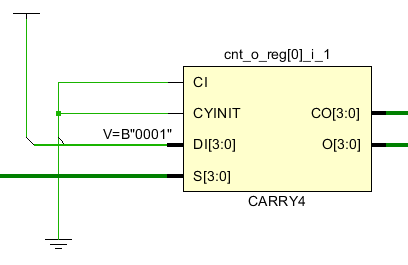

采用RTL代码描述位宽相同的两个数相加或相减,无论是有符号数还是无符号数,Vivado综合后的结果是一致的。以32bit数据为例,相应的代码如下图所示。这里考虑到两个32bit数据相加其结果可能为33bit

2020-09-27 15:17

前文曾经指出,Wishbone总线规范是"轻量级(Lightweight)"规范,它实现起来非常简单紧凑,接口需要的互联逻辑非常少。这里给出一个Wishbone从设备的一个例子,如图21所示。该从设备由一个与门和8个D触发器构成。在写周期,当STB_I和WE_I同时有效,数据DAT_I[7:0]在时钟CLK_I的上升沿被写到触发器中。

2018-07-31 09:11

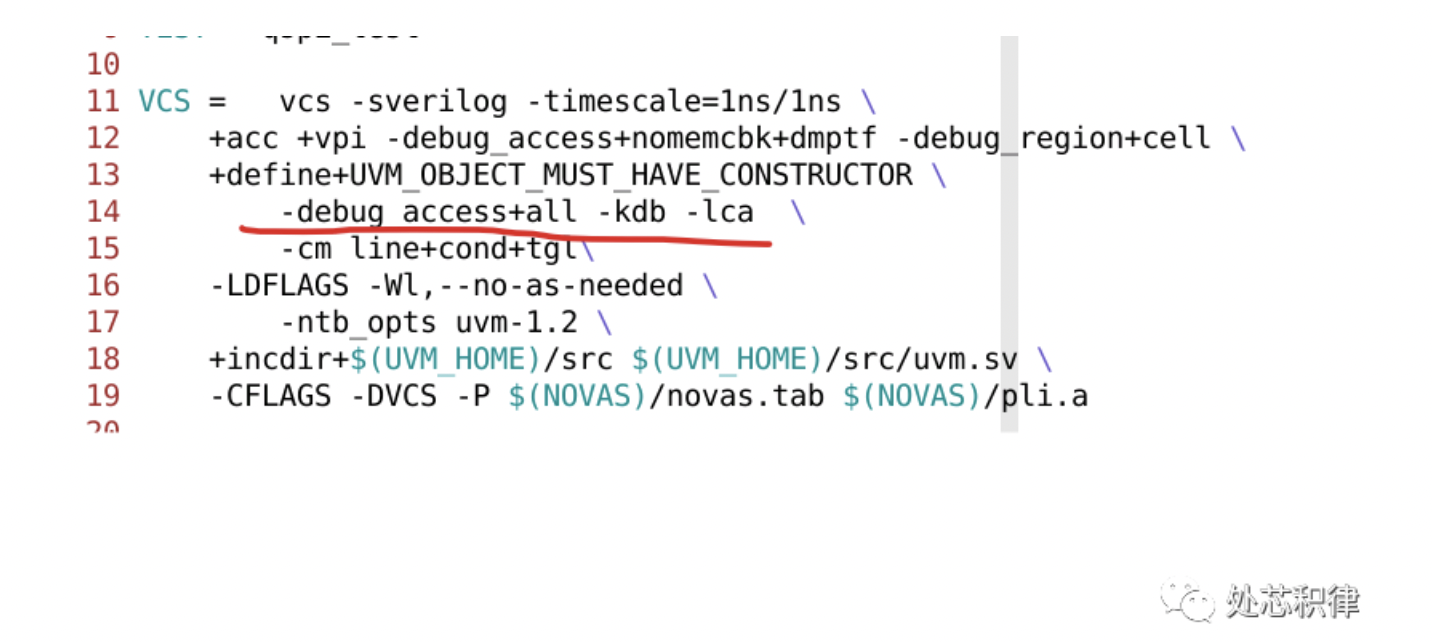

我们常用的debug UVM的方法是通过打印log实现。有没有办法像 debug RTL代码一样将 UVM 中变量拉到波形上看呢?答案是有的,下面让我们看看是怎么做到的。

2023-06-29 15:14

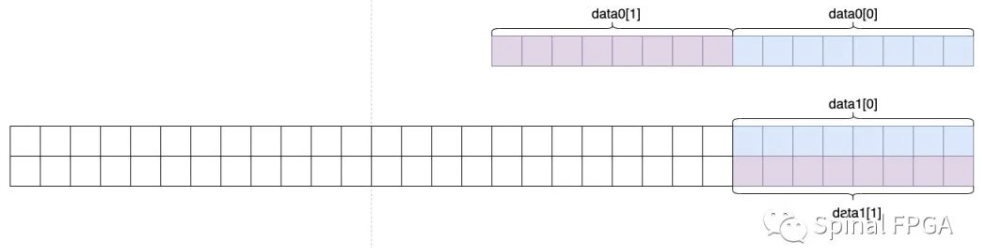

数直接相加此方案对应的电路图如下图所示。这里不难看出关键路径是三个加法器所在路径,这将是时序收敛的瓶颈。 此电路对应的SystemVerilog代码如下图所示。 从综合后的结果来看,逻辑级数最高为7。 第二种方案:加法树 加法树的结构如下图所示,两两相加。与第一种方案相比

2020-09-24 14:02

并不是因为上述.vh代码不存在,而是由于^M换行符的存在造成的错误。gvim怎么显示^M换行符呢?这里介绍几种方法。

2024-03-18 10:36