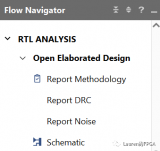

在Vivado FlowNavigator中有一个Elaborated Design,如下图所示,属于RTL Analysis这一步对应的设计。可能很多工程师都没有使用到,而实际上对于代码优化,它是很有帮助的。

2020-10-21 10:56

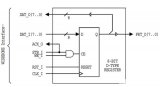

前文曾经指出,Wishbone总线规范是"轻量级(Lightweight)"规范,它实现起来非常简单紧凑,接口需要的互联逻辑非常少。这里给出一个Wishbone从设备的一个例子,如图21所示。该从设备由一个与门和8个D触发器构成。在写周期,当STB_I和WE_I同时有效,数据DAT_I[7:0]在时钟CLK_I的上升沿被写到触发器中。

2018-07-31 09:11

并不是因为上述.vh代码不存在,而是由于^M换行符的存在造成的错误。gvim怎么显示^M换行符呢?这里介绍几种方法。

2024-03-18 10:36

在三天前SpinalHDL1.8.0正式上线,在这次更新中增加了Scala代码和生成的RTL代码之间的对照功能,也就是说我们可以在生成的RTL

2022-12-09 10:32

利用工具将RTL代码转化为门级网表的过程称为逻辑综合。综合一个设计的过程,从读取RTL代码开始,通过时序约束关系,映射产生一个门级网表。

2022-11-28 16:02

perips目录主要用于存放各种外设(Peripherals)模块的Verilog RTL代码,譬如GPIO,UART,SPI等。大部分的Peripherals的Verilog RTL

2018-11-26 17:23

当在SpinalHDL中调用别人的RTL代码时,需要采用BlackBox进行封装。对于大多数场景,想必小伙伴们都已轻车熟路。今天着重来看下当RTL代码的接口中存在数组形

2023-05-22 10:04

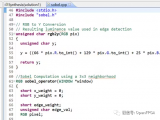

用工具用 C 生成 RTL 的代码基本不可读。以下是如何在不更改任何 RTL 的情况下提高设计性能。

2023-10-30 11:41

一个完整的半定制设计流程应该是:RTL代码输入、功能仿真、逻辑综合、形式验证、时序/功耗/噪声分析,布局布线(物理综合)、版图验证。

2018-11-24 09:17

我们常用的debug UVM的方法是通过打印log实现。有没有办法像 debug RTL代码一样将 UVM 中变量拉到波形上看呢?答案是有的,下面让我们看看是怎么做到的。

2023-06-25 16:01