本篇文章是关于相位锁定环(PLL)频率合成器的设计和分析,重点讨论了相位噪声和频率噪声的测量、建模和仿真方法。文章以设计一个假想的PLL频率

2023-10-26 15:30

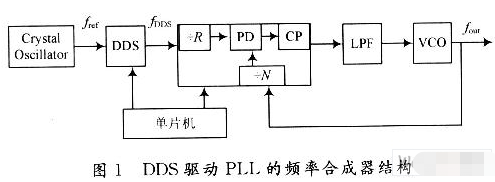

摘 要:结合数字式频率合成器(DDs)和集成锁相环(PLL)各自的优点,研制并设计了以DDS芯片AD9954和集成锁相芯片ADF4113构成的高分辨率、低杂散、宽频段频

2012-06-25 13:53

您曾设计过具有分数频率合成器的锁相环(PLL)吗?这种合成器在整数通道上看起来很棒,但在只稍微偏离这些整数通道的频率点上杂散就会变得高很多,是吧?如果是这样的话,您

2023-04-18 09:29

结合数字式频率合成器(DDs)和集成锁相环(PLL)各自的优点,研制并设计了以DDS芯片AD9954和集成锁相芯片ADF4113构成的高分辨率、低杂散、宽频段频率

2021-06-08 14:07

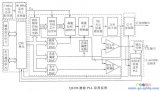

随着高速集成工艺技术的发展,锁相频率合成器的集成化程度已大大提高。目前已出现了一系列将高速前置合频器集成在片内的单片集成频率合成器芯片。例如美国Motorola公司的MC145190/191/192

2021-06-18 10:52

MAX2902 ISM发送器设计用于与外部频率合成器IC组合,形成完整的TX路径方案。根据系统要求,可以使用小数N分频或整数N分频频率合成器IC。了解两种频率合成器的通道步长、相位噪声和

2023-03-03 15:22

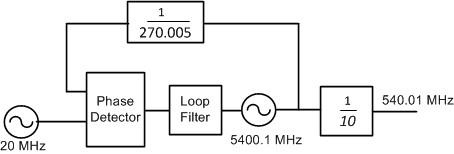

频率合成器在锁相环 (PLL) 中工作,其中相位/频率检测器 (PFD) 将反馈频率与参考频率的分频版本进行比较(图 1)。PFD的输出电流脉冲经过滤波和积分以产生电压。该电压驱动外部压控振荡器 (VCO) 增加或降低输出频率,从而将 PFD 的平均输出驱动至零。

2023-02-03 10:50

下图所示的是用 Q2230 激励锁相倍频系统实现的一个实际的 频率合成器 。系统时钟采用40 MHz,这样能输出DC~15 MHz、分辨率为0.01 Hz、电压峰一峰值为10 V的正弦波。谱纯度优于

2018-03-17 11:13

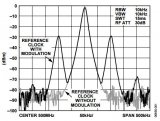

直接数据频率合成器(DDS)因能产生频率捷变且残留相位噪声性能卓越而著称。另外,多数用户都很清楚DDS输出频谱中存在的杂散噪声,比如相位截断杂散以及与相位-幅度转换过程

2019-11-14 17:10

频率合成器是现代无线通信设备中一个重要的组成部分,直接影响着无线通信设备的性能。频率合成技术历经了早期的直接合成技术(DS)和锁相

2018-06-01 08:27