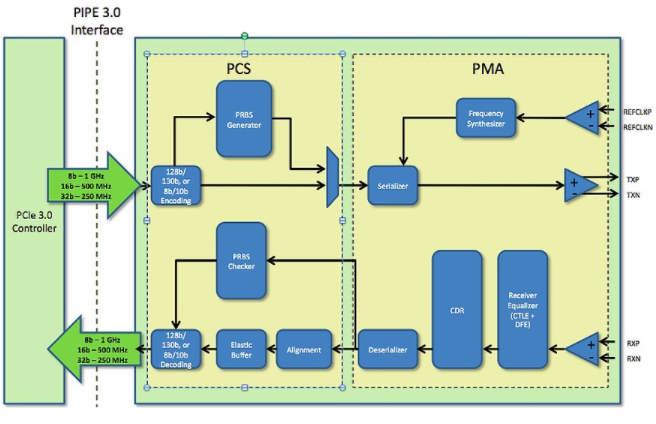

Xilinx7系列FPGA集成了新一代PCI Express集成块,支持8.0Gb/s数据速率的PCI Express 3.0。本文介绍了7系列FPGA PCIe Gen3的应用接口及一些特性。

2024-11-05 15:45

借助128b/130b 编码方案和加扰多项式,PCIe Gen3 提出了许多传输和接收问题,所有这些问题都在最新规范中得到解决。

2022-06-14 15:27

Altera公司(Nasdaq: ALTR)宣布,成功实现28-nm Stratix® V GX FPGA与PLX®技术公司(Nasdaq: PLXT) ExpressLane™ PCI Express® (PCIe®) Gen3的互操作

2011-12-14 09:28

Compute Express Link 是一种缓存一致性互联,旨在帮助系统(尤其是具有加速器的系统)更高效地运行。CXL位于 PCIe Gen5链路基础架构之上。可以有 PCIe

2022-03-23 15:26

查看UltraScale FPGA中集成的PCIe Gen3模块的性能演示。 第一个演示显示了PCIe链路上的最大数据吞吐量; demo#2利用现成的DMA引擎和软件驱动程序来代表典型的用例。

2018-11-28 06:22

Altera公司 (NASDAQ: ALTR)今天宣布,其28 nm Stratix® V GX FPGA已经收录在最新的PCI-SIG® Integrators名录中,符合PCI Express® (PCIe®) 3.0规范(Gen3)要求。

2013-05-23 10:34

Exascend PI3(PCIe Gen3x4)产品系列是工业级(-40°C〜85°C工作温度)SSD,具有企业级性能(保持高速和低延迟),可提供标准U.2(最高8TB),M.2 2280(最高4TB)可用。

2020-12-30 14:32

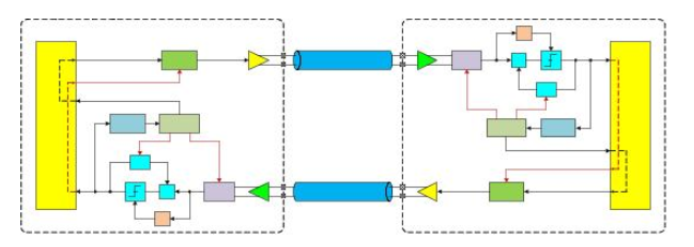

在PCIe 3.0和4.0中的链路均衡技术相较于先前代要复杂得多,这样一种动态均衡技术可以分为两个方面进行讨论。

2020-04-07 11:24

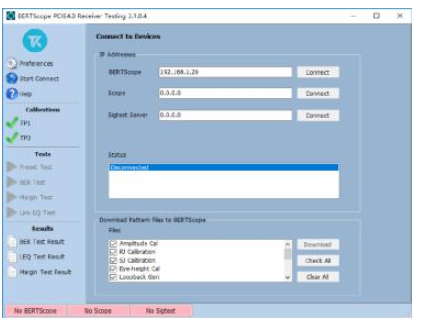

在PCIe 2.0的时代,通常只要保证了发送端的信号质量,那么整个系统也就能够正常工作;因此接收端测试并不是必测项。

2020-04-09 11:10

与固态介质一起使用,并使数据能够以闪存本身的完整读/写速度存储。虽然前几代数据记录仪具有SATA接口,或者在存储之前将PCIe转换为SATA,但当今最先进的数据记录仪使用NVMe内存来减少延迟并提高带宽。

2022-11-15 16:33