这几款游戏都是目前比较热门的游戏大作,有着大型的场景需要加载。因此测试以点击进入游戏开始计时,到完全进入可操作界面为止,分别进行时间统计。

2018-05-16 17:12

)和SFF-8612(设备端)连接器,OCuLink接口支持原生PCIe通道传输协议。它的核心使命是直接、无损地“延伸”设备内部的PCIe通道,将

2025-08-29 11:24 ICY DOCK硬盘盒 企业号

得不考虑一个问题,芯片组提供的接口和CPU直连接口相比,会不会有性能下降呢? 也许有些小伙伴看到前面一段话还有点懵,啥?M.2接口还不一样吗?没错,在很多主板上的多个M.2接口,确实有连接通道的差别,所谓直连M.2接口,一般是使用CPU自带的PCIe

2020-09-01 15:05

随着英特尔Alder Lake CPU的发布,以及AMD 7000 Ryzen CPU的即将发布,PCIe 5.0 硬件终于成为现实。但什么是 PCIe 5.0?

2023-11-18 16:48

的,旨在替代旧的PCI,PCI-X和AGP总线标准。PCIe属于高速串行点对点双通道高带宽传输,所连接的设备分配独享通道带宽,不共享总线带宽,主要支持主动电源管理,错误报告,端对端的可靠性传输,热插拔以及服务质量(Q

2018-10-03 12:55

和PCIe一样,SATA也有独立的发送和接收通道,但与PCIe工作模式不一样:同一时间,只有一条道可以进行数据传输,也就是说,你在一条道上发送数据,另外一条道上不能接收数据,反之亦然。这种工作模式是半双工模式。

2018-06-25 10:54

两个设备间,其是一种基于数据包、串行、点对点的互连,因此所连接设备独享通道带宽。根据使用的版本号和通道数,其性能具有可扩展性。对于PCIe 2.0,每条通道在每个方向上

2018-10-30 17:18

该信号为全局复位信号,由处理器系统提供(RC),处理器系统需要为PCIe插槽和PCIe设备提供该复位信号。PCIe设备使用该信号复位内部逻辑。当该信号有效时,PCIe设

2018-12-22 14:45

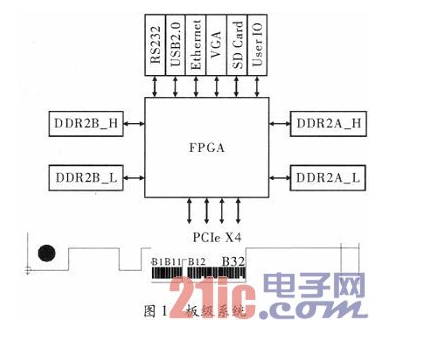

如图所示,PCIe IP作为endpoint与RC对接,用户实现了应用逻辑,与PCIe IP进行交互,交互信号中data格式为TLP报文格式,且交互信号包含相应的控制信号,例如PCIe配置空间和IP相干的配置信号。

2024-02-26 18:19