系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的时钟发生器件的选择上往往少有考虑。然而,如果不慎重考虑时钟发生器的相位噪声和抖动性能,数据转换

2020-11-22 11:34

时钟合成器和时钟发生器是两种用于产生时钟信号的电子器件,它们在功能和应用上有一些区别。

2023-11-09 10:26

Xilinx7系列FPGA集成了新一代PCI Express集成块,支持8.0Gb/s数据速率的PCI Express 3.0。本文介绍了7系列FPGA PCIe

2024-11-05 15:45

本内容介绍了PCI总线/PCI-X接口及PCI-PCI-Express的知识,讲解了从PCI、PCI-X到

2012-06-05 16:16

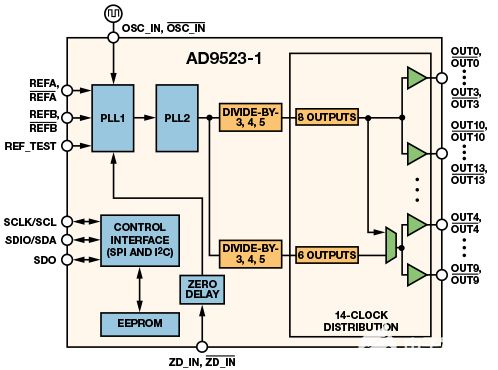

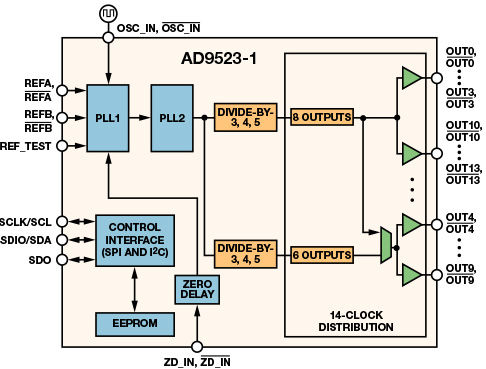

AD9523、AD9523-1和AD9524时钟发生器(如图1所示)由两个串联的模拟PLL组成。第一个PLL(PLL1)清除参考抖动,而第二个PLL(PLL2)产生高频相位对齐输出。PLL2 还可以产生高基频,从中可以导出各种较低频率。

2023-02-02 17:29

本文讨论电源噪声干扰对基于PLL的时钟发生器的影响,并介绍几种用于评估由此产生的确定性抖动(DJ)的测量技术。派生关系显示了如何使用频域杂散测量来评估时序抖动行为。实验室台架测试结果用于比较测量技术,并演示如何可靠地评估参考时钟发生器的电源噪声抑制(PSNR)性能

2023-04-11 11:06

PCI-Express 电路板可实现 Miami SoM 与标准 PC 的无缝集成,为基于 FPGA 的协处理器提供极高的处理性能。除 PCI-Express 接口外,该电路板还支持用于远程及本地云

2018-07-04 03:34

这是带有板上芯片(COB)的1Hz时钟发生器电路。通常,为数字时钟和计数器电路应用产生1Hz时钟的电路将IC与晶体和微调电容器等结合使用。

2022-06-07 10:43

系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的时钟发生器件的选择上往往少有考虑。

2019-08-07 17:51

。表2所示为ADIsimCLK在这些设置下生成的PLL1环路滤波器值。##图6和图7展示的是AD9523-1 PLL1输出,其相位噪声比图2中的高噪声参考频率分别高出6

2014-03-25 11:38