超高速ADC通常采用LVDS电平传输数据,高采样率使输出数据速率很高,达到百兆至吉赫兹量级,如何正确接收高速LVDS数据成为一个难点。本文以ADS42LB69芯片的数据

2017-11-17 10:40

。使用lvds来接收高速ADC产生的数据会很方便。像ISERDES,IDDR,IDELAY,OSERDES,ODDR这种资源在FPGA的IOB中多得是(每个IO都对应有

2018-06-30 10:23

LVDS已广泛应用于接口器件和现场可编程门阵列(FPGA)、专用集成电路(ASIC)中,采用LVDS的系统成功实现了高速互连。然后,并非所有的

2021-05-23 17:29

在《做信号链,你需要了解的高速信号知识(一)》中,我们探讨了LVDS和JESD204B标准的优势,这些标准在

2024-07-03 10:29

SAR ADC是一个非常常见的拓扑结构,这是一种在速度、分辨率和功率之间提供了很好平衡的折衷方案。SAR ADC的一个关键优势是几乎没有延迟。因此在很多应用领域都能看到

2022-04-28 12:53

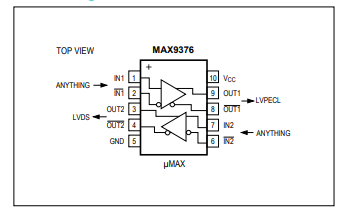

MAX9376是全差分、高速、LVDS/任何输入至LVPECL/LVDS双通道转换器,适用于高达2GHz的信号速率。一个通道是LVDS/任何输入至LVPECL转换器,另

2025-05-16 14:57

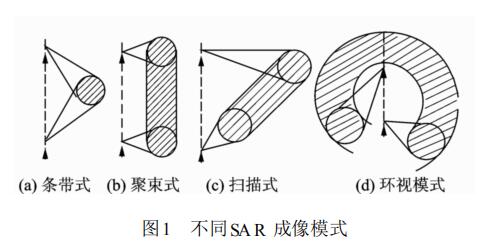

环视合成孔径雷达(SAR) 图像用于导弹精确末制导中的景象匹配处理, 需要满足几何精度的要求。校正由雷达平台不规则运动和天线圆周扫描导致的图像几何失真, 是环视SAR 成像处理

2018-03-13 09:07

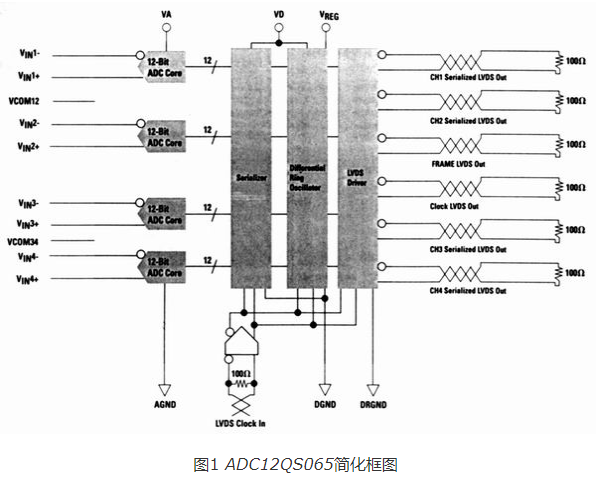

在输入信号转换数字数据之后,必须传输它们到DSP或ASIC/FPGA进行处理。流行的全差分输出信号传输是方便的。全差分的输出信号通过两条对称线给出和吸收电流。这种信号传输的一个例子是LVDS(低压差分信号)格式。ADC12QS065

2020-04-04 17:43

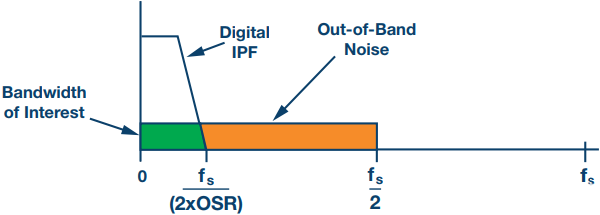

在之前的一些文章中,Δ-Σ和SAR(逐次逼近寄存器)ADC的一般概述中,已经涵盖了与信噪比(SNR)和有效位数(ENOB)相关的过采样技术。过采样技术最常用于 Δ-Σ

2023-01-08 21:08

32 位分辨率的过采样 SAR ADC。在设计高性能以利用ADC性能时,整个信号链需要非常低的噪声。当信号链需要额外的隔离时,性能将受到影响。

2023-02-15 10:39