我们在对FPGA项目进行约束的时候,常常看到这样的电平标准,例如LVCOM18,LVCOS25,LVDS,LVDS25等等,其实这些都是一系列的

2020-08-24 17:32

M-LVDS:英文全称Multipoint-Low-Voltage DifferentialSignaling,中文全称:多点低电压差分信号,其主要目的是将点对点的LVDS延申用于解决多点应用问题,因此其除了LVDS

2023-11-22 16:29

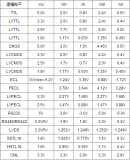

由于各种逻辑电平的输入、输出电平标准不一致,所需的输入电流、输出驱动电流也不同,为了使不同逻辑电平能够安全、可靠地连接,逻辑电平

2022-11-10 10:01

输入高电平门限Vih:保证逻辑门的输入为高电平时所允许的最小输入高电平,当输入电平高于Vih时,则认为输入电平为高

2018-03-10 09:47

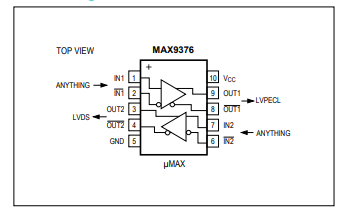

MAX9376是全差分、高速、LVDS/任何输入至LVPECL/LVDS双通道转换器,适用于高达2GHz的信号速率。一个通道是LVDS/任何输入至LVPECL转换器,另一个通道是

2025-05-16 14:57

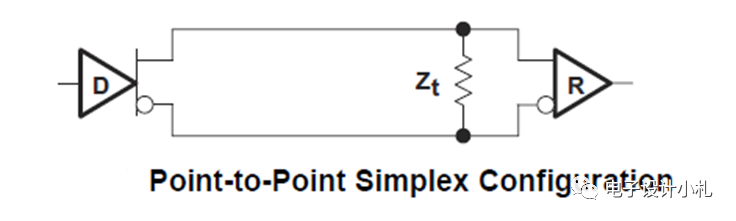

分线路驱动器。LVDS技术将传统5V差分标准电平(如TIA/EIA - 422B)的输出电压降低,从而降低了功耗,提高了开关速度,并且能够在3.3V电源轨下工作

2025-12-29 16:25

作为一名电子设计的硬件工程师,电平转换是每个人都必须面对的的话题,主芯片引脚使用的1.2V、1.8V、3.3V等,连接外部接口芯片使用的1.8V、3.3V、5V等,由于电平不匹配就必须进行电平转换

2020-03-09 10:40

SNx5LVDS3xxxx系列器件满足或超越了ANSI TIA/EIA - 644标准的要求,实现了LVDS的电气特性。该技术将5 - V差分标准

2026-01-04 14:20

超高速ADC通常采用LVDS电平传输数据,高采样率使输出数据速率很高,达到百兆至吉赫兹量级,如何正确接收高速LVDS数据成为一个难点。本文以ADS42LB69芯片的数据接收为例,从信号传输和数据解码两方面,详述了实现

2017-11-17 10:40

很多工程师在使用Xilinx开发板时都注意到了一个问题,就是开发板中将LVDS的时钟输入(1.8V电平)连接到了VCCO=2.5V或者3.3V的Bank上,于是产生了关于FPGA引脚与LVDS(以及

2020-10-10 09:25