IBIS(缩写Input/Output Buffer Information Specification):输入输出缓冲器,对输入输出端口快速准确建模,便于仿真。

2024-05-11 09:09

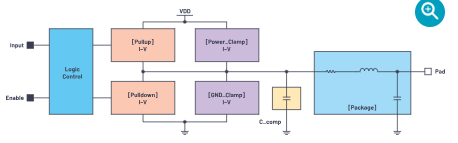

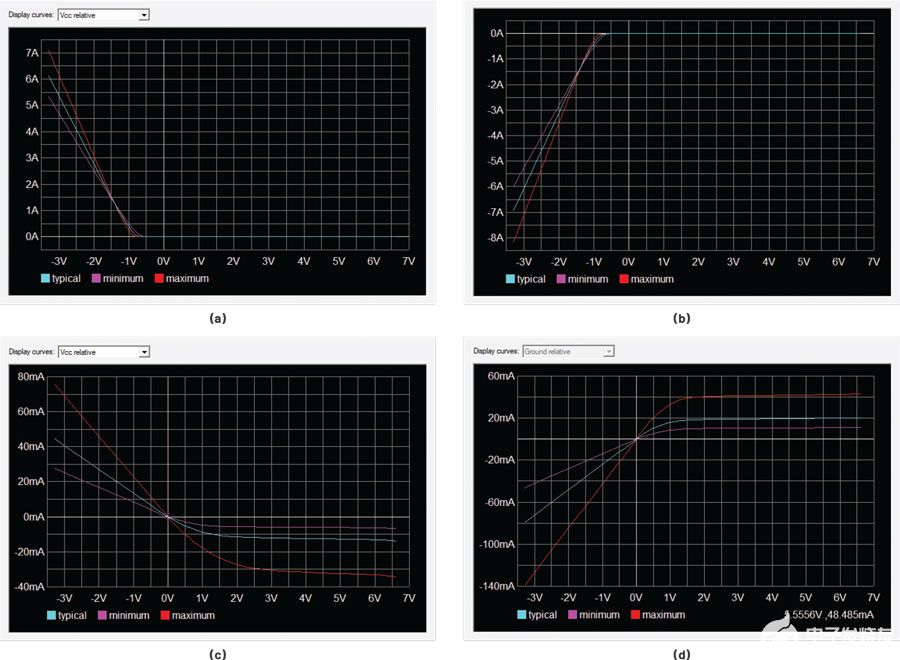

本文介绍如何使用LTspice来提取数据和构建IBIS模型。还提出通过定性FOM和曲线面积度量的定量FOM将IBIS模型与参考SPICE模型关联起来的方法。这样就可以让用户确信IBIS模型的行为

2023-06-15 17:06

IBIS表示输入/输出缓冲器信息规范。它代表了IC供应商提供给客户进行高速设计仿真的器件的数字引脚的特性或行为。这些模型使用IBIS开放论坛——负责管理和更新IBIS模型规范与标准的行业组织——所

2023-06-15 16:32

半导体LSI的EDA模型之一是"IBIS模型",完整称为Input/OutputBuffer Information Specification,是一个描述数字IC输入端和输出端电气特性的文本文件,在电路仿真中被广泛使用。IBIS模型由封装模型

2023-07-14 10:10

IBIS 代表 输入/输出缓冲器信息规范。它表示IC供应商提供给其客户以用于高速设计仿真的器件数字引脚的特性或行为。这些模型使用IBIS开放论坛指定的参数模拟设备的I/O行为,IBIS开放论坛是一个管理和更新

2022-12-15 11:55

当半导体厂商被索要SPICE模型时,他们并不愿意提供,因为这些模型会包含有专有工艺和电路信息。这个问题已经通过采用IBIS模型来 (输入/输出缓冲器信息规范)解决,IBIS也被称为ANSI/EIA-656,这是一个建模的新标准,在系统设计人员中越来越流行。

2023-10-31 09:44

本文聚焦IBIS(I/O Buffer Information Specification)模型中的Corner(Typ/Min/Max)参数处理,系统分析Corner的定义规则及其对信号完整性

2025-04-23 16:10

本人最早接触SI仿真的时候,只是进行一个简单的流程操作,其中涉及到的原理、模型知之甚少,再后来慢慢的接触到了深一点的东西开始自己搭建电路了解到了IBIS。用于电路仿真的模型有好多,可能IBIS是最常

2022-07-21 09:02

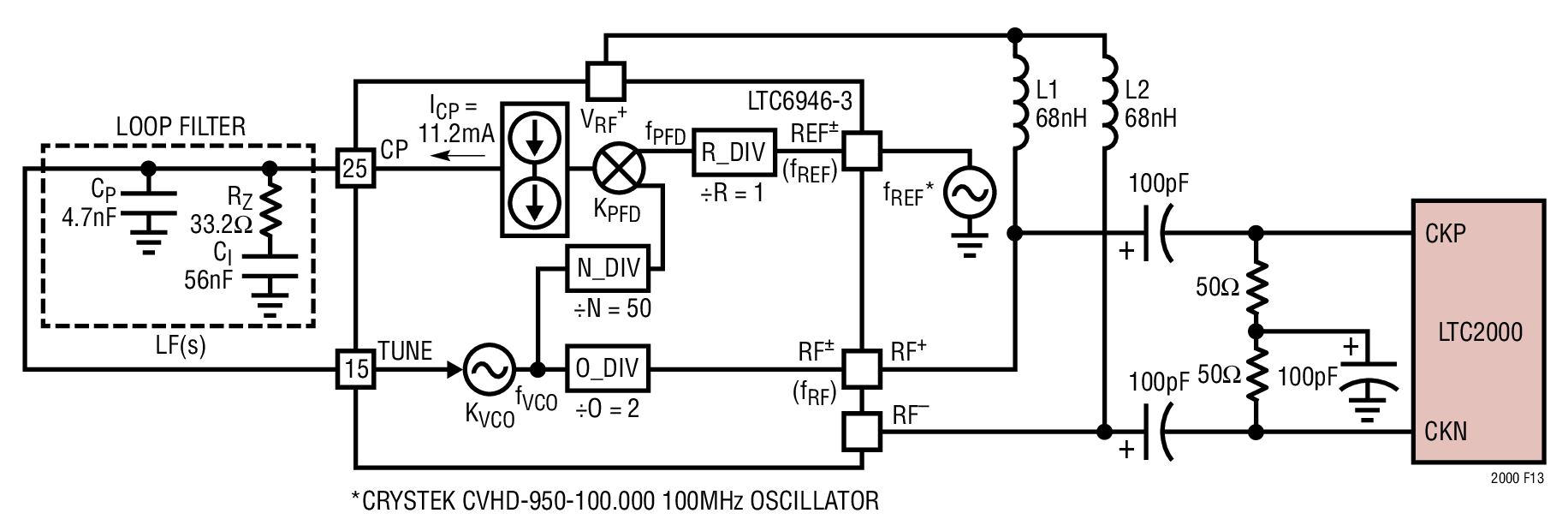

了 VCO 的超低噪声和超低寄生 0.37GHz 至 6.39GHz 整数 N PLL 合成器 LTC6946 怎样才能实现这样的目标。

2017-09-11 10:59

最大化频段中可能的通道数至关重要。高速DAC需要一个干净的采样时钟,以实现最佳的噪声和杂散性能。使用 LTC6946 杂散 PLL 频率合成器作为 LTC2000 的时钟源可最大限度地提高系统性能(图 1)。

2023-01-05 15:55