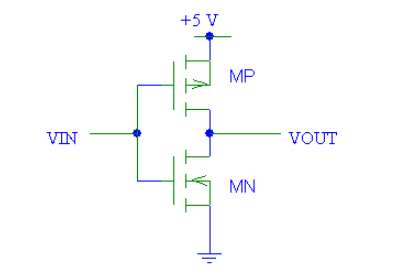

参考上面的CMOS反相器图,由于CMOS器件输入端的电压在5伏和0伏之间变化,因此PMOS和NMOS的状态将相应地不同。

2021-01-21 11:37

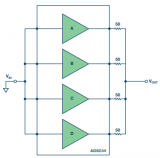

想要降低系统中增加的噪声,必须降低电压噪声。常用方法——并联放置多个缓冲器可降低电压噪声。但是,该方法会使偏置电流、电流噪声

2018-05-27 05:13

的扇出型缓冲器,是一种将一路时钟源信号通过频率复制生成多路时钟信号的器件,通常时钟缓冲器还兼具有时钟分配,格式转换和电平转换的功能。 对于需要多路时钟信号的电子系统来说,时钟源加时钟

2022-10-18 18:36

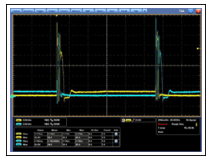

LTC6416 是一款差分单位增益缓冲器,专为以极低的输出噪声和卓越的线性 (在超过300MHz 的频率条件下) 来驱动 16 位 ADC 而设计。差分输入阻抗为 12kΩ,因而允许在输入端上使用 1:4 和 1:8

2025-03-14 17:32

三态数据缓冲器是数据输入/输出的通道,数据传输的方向取决于控制逻辑对三态门的控制。本文介绍三态缓冲器的逻辑符号。

2018-01-11 10:42

LTC6417 是一款差分单位增益缓冲器,能够以极低的噪声和卓越的线性度来驱动一个 50Ω 负载。 该器件非常适合于采用频率范围为 DC 至高于 600MHz 的输入信号来驱动高速 14 位和 16

2025-03-13 11:35

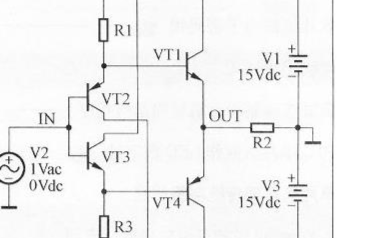

MAX13256具有可调过流门限,用于短路保护。不幸的是,这个阈值使得使用标准方法为设备设计缓冲器变得困难。本应用笔记介绍了如何为MAX13256设计电压缓冲器,同时考虑限流特性。

2023-06-25 14:22

HMC7043是一种高性能时钟缓冲器,用于为具有并行或串行(JESD204B型)接口的高速数据转换器分配超低相位噪声参考

2023-05-31 10:47

buffer缓冲器电路图与buffer电路示意图 buffer缓冲器的作用 buffer译名为: 缓冲,缓冲器,缓冲液;

2022-10-18 19:01

本文讨论了将低失真、低噪声、高速放大器用作DAC缓冲器的一些优势,并将其性能与变压器进行了比较.同时比较了采用两种不同架构的三类应用电路

2012-06-13 11:17